# 4

## ADS 在信号完整性分析中的应用

### 4.1 ADS 的基本使用

#### 4.1.1 ADS 主要操作窗口

##### 1. 主窗口

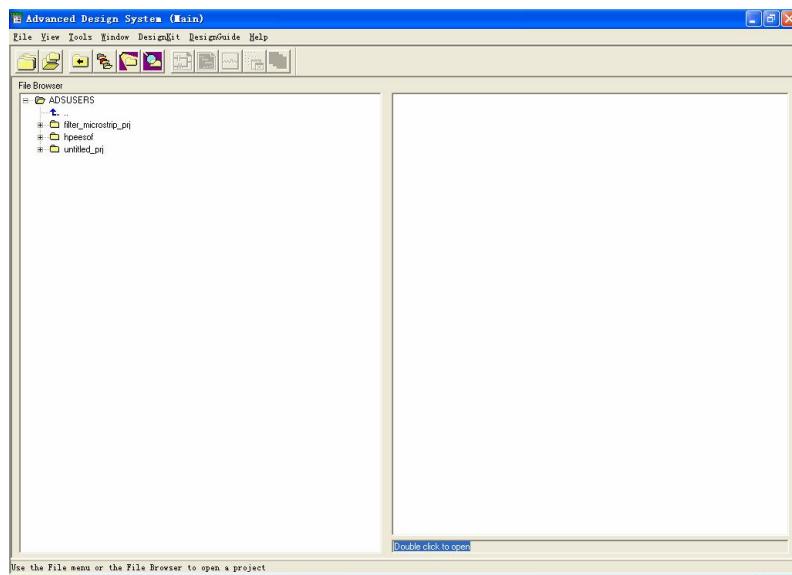

打开 ADS，将弹出 ADS 的主窗口，如图 4-1 所示。ADS 主窗口主要用来创建或打开工程，进行文件管理、工程管理等。它主要包含菜单栏、工具栏、文件浏览器区和工程管理区等几个部分。

图 4-1 ADS 主窗口

##### 2. 原理图设计窗口

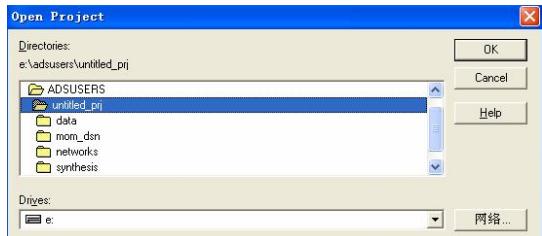

单击 File→Open Project 打开一个已存在的工程文件，或者创建一个新的工程文件，如图 4-2 所示。

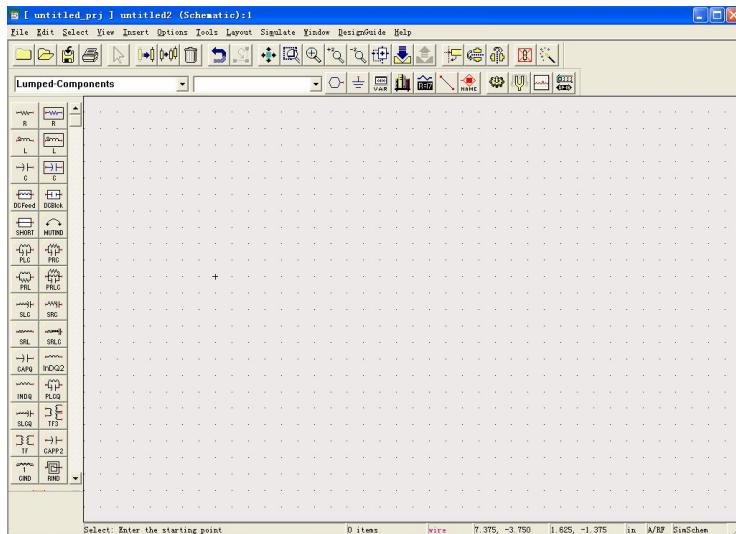

将打开一个原理图设计窗口，如图 4-3 所示。原理图设计窗口包含标题栏、菜单栏、工具栏、元件面板列表、元件面板、画图区等。在该窗口可以进行电路的设计和分析。

## 信号完整性仿真分析方法

图 4-2 Open Project 对话框

图 4-3 原理图设计窗口

### 3. 布局图设计窗口

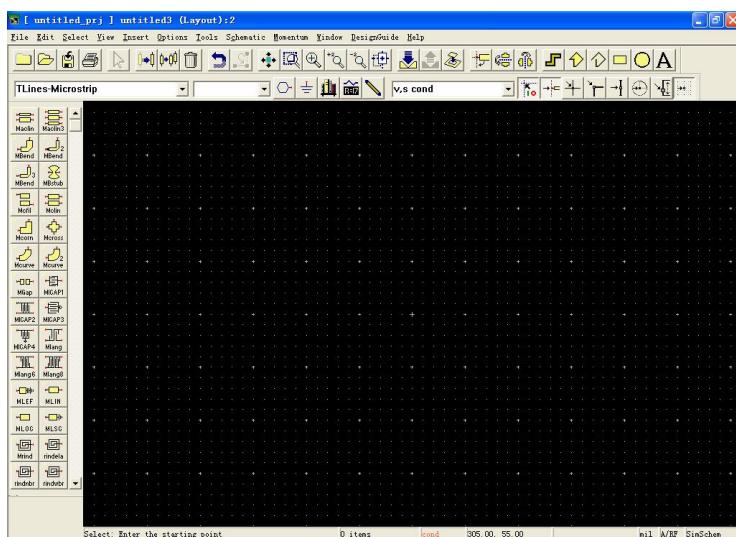

布局图设计窗口用来进行布局图的设计、编辑和仿真，如图 4-4 所示。布局图设计窗口与原理图设计窗口的内容基本相同。

图 4-4 布局图设计窗口

#### 4. 数据显示窗口

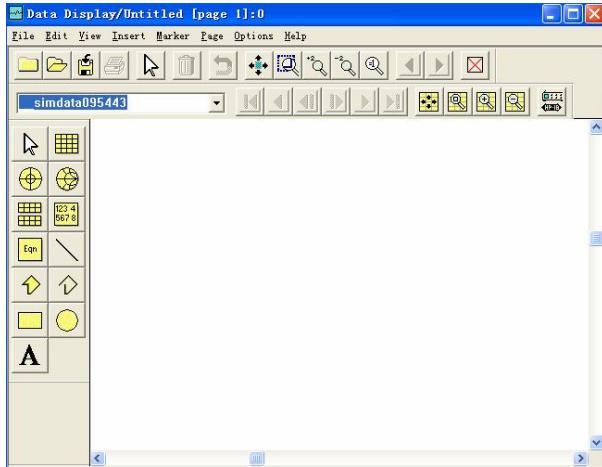

数据显示窗口用来显示仿真的结果，也可以显示从其他数据源获取得到的数据。数据显示窗口包括标题栏、菜单栏、工具栏、数据来源列表和数据显示方式面板等。如图 4-5 所示。

图 4-5 数据显示窗口

#### 4.1.2 ADS 基本操作

本节以一个简单的电路分析为例介绍 ADS 的基本操作步骤。

##### 1. 建立电路模型

###### (1) 添加三极管及其模型并设置参数

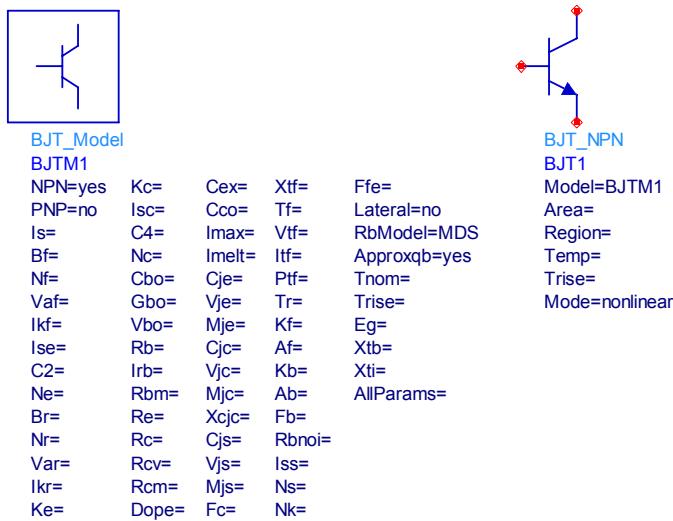

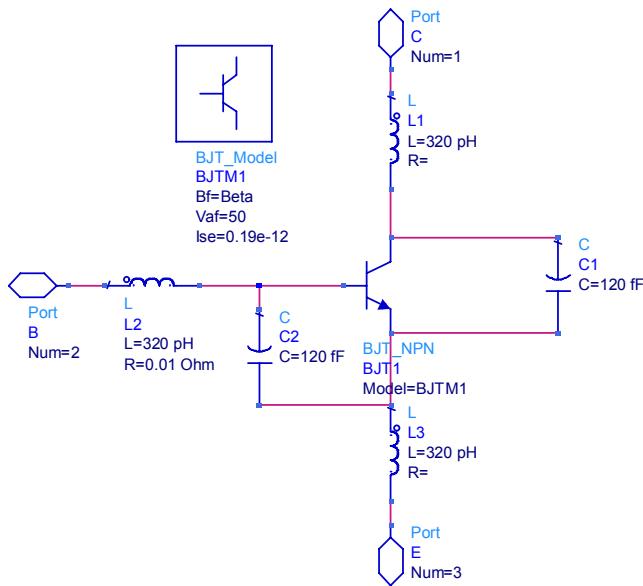

- 1) 在原理图设计窗口中选择 Devices-BJT 元件面板列表，选择元件 BJT\_NPN 放入原理图中。

- 2) 同样在 Devices-BJT 元件面板列表中选择 BJT\_Model 放入原理图中，如图 4-6 所示。

图 4-6 插入 BJT 模型

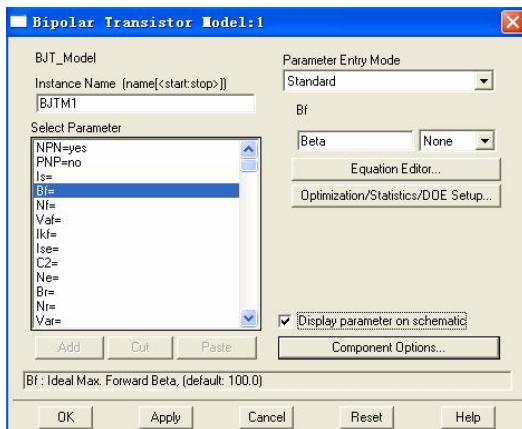

- 3) 双击 BJT\_Model 模型，出现参数设置对话框，单击 Component Options 按钮，在弹出窗口

中的 Parameters Visibility 栏中选择 Clear All, 单击 OK 按钮, 然后单击 Apply 按钮, 可以看到原理图中的参数列表已经被清空。

4) 接着, 在 BJT\_Model 参数设置对话框中对模型参数进行设置。选择参数 Bf, 设置其值为 Beta, 并选中复选框 Display parameter on schematic, 单击 Apply, 此时 Beta 已成为电路的一个参数, 如图 4-7 所示。

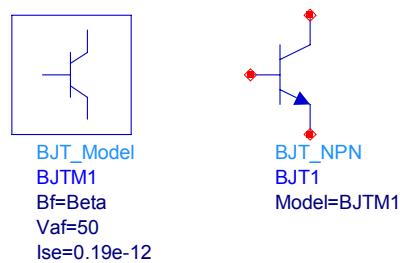

- 5) 设置 Vaf (预置电压) =50, 同样选中 Display parameter on schematic 复选框。

- 6) 设置 Ise (EB 两极漏电流) =0.19e-12, 并选中 Display parameter on schematic, 单击 OK 按钮, 此时模型就有了一些实际参数, 如图 4-8 所示。

图 4-7 模型参数设置

图 4-8 完成参数设置后的模型

7) 按照同样的方法去掉 BJT\_NPN 元件中的一些不希望显示的参数, 如区域、面积、模式和温度等, 如图 4-8 所示。

#### (2) 加入寄生元件并设置端口

本节加入代替三极管寄生参数的电感和电容元件, 并加入相应的连接部分。

1) 在原理图设计窗口中的 Lumped-Components 列表中选择 3 个电感 L 和 2 个电容 C 插入到电路图中。

2) 设置电感值为 320pH, 电容值为 120fF, 这里要注意电感和电容的单位。并将其中一个电感的 R 参数设置为 0.01Ω。

3) 放置端口并命名。单击工具栏中的 Insert Port 按钮, 在原理图中插入 3 个端口, 并分别命名为 C、B 和 E。它们分别代表三极管的集电极 (C)、基极 (B) 和发射极 (E)。

#### 4) 按照图 4-9 连接各个元件。

#### (3) 创建电路符号

下面将把图 4-9 中的电路建成一个符号。这里使用 ADS 内部的 BJT 符号, 方法如下:

- 1) 在原理图窗口中选择 View→Create/Edit Schematic Symbol, 出现 Symbol Generator 对话框, 单击 OK 按钮, 默认符号就会出现。

- 2) 默认符号出现后, 在菜单栏中选择 Select→Select All, 并单击 Delete 删除默认符号。

- 3) 在原理图窗口中选择 View→Create/Edit Schematic 命令, 回到原理图设计窗口中。

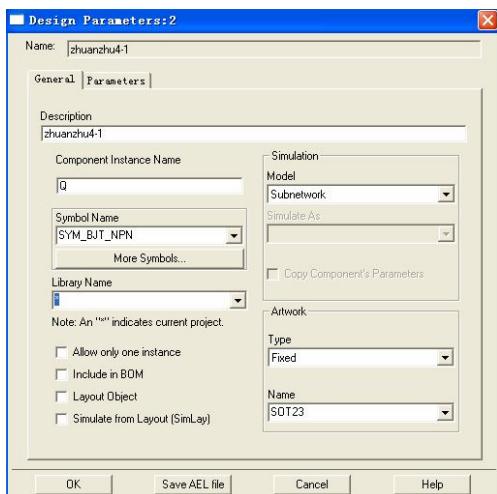

- 4) 在原理图窗口中选择 File→Design Parameters, 打开 Design Parameters 对话框。

- 5) 选择 Design Parameters 对话框中的 General 选项卡, 对参数进行修改:

图 4-9 带有寄生元件和端口的原理图

- ①在 Component Instance Name 框中改变元件名为 Q。

- ②单击 Symbol Name 框旁边的下拉箭头，选择符号 SYM\_BJT\_NPN。

- ③在布线模型 Artwork 栏的 Type 和 Name 中分别选择 Fixed 和 SOT23，如图 4-10 所示。

- 6) 单击 Save AEL file 按钮，写入修改值。

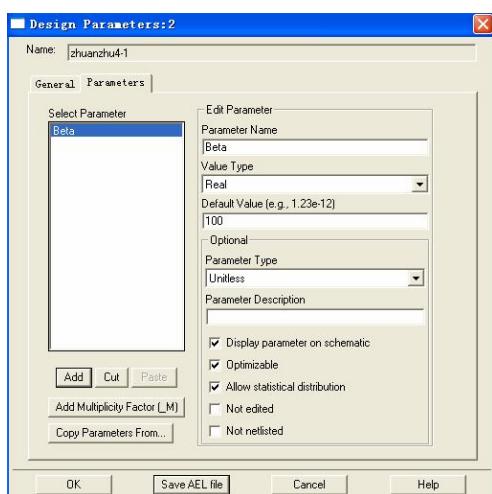

- 7) 单击 Parameter 选项卡，在 Parameter Name 框中输入 Beta，在 Default Value 框中输入 100，单击 Add 按钮，将参数添加到模型中去。选中 Display parameter on schematic 框，单击 OK 按钮保存设置，并关闭对话框，如图 4-11 所示。

图 4-10 内建符号设置

图 4-11 给符号添加参数

- 8) 单击 Save 按钮保存原理图，电路符号就创建完毕了。

#### (4) 插入电路符号

在原理图中添加这个新建的电路符号的过程如下：

- 1) 打开一个新的原理图设计窗口，并命名为 dc\_curves

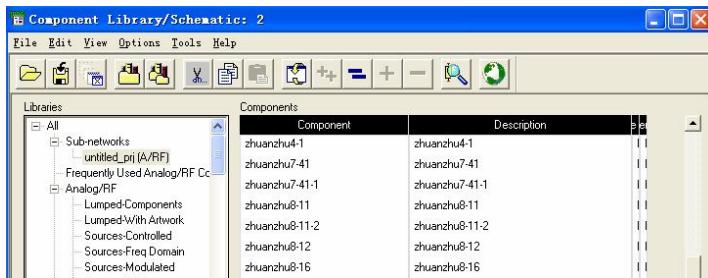

- 2) 单击 Display Component Library List 按钮 ，弹出 Component Library/Schematic 窗口，如图 4-12 所示。

图 4-12 插入电路符号 zhuanzhu4-1

- 3) 在 Components 窗口中选择 zhuanzhu4-1，并单击 zhuanzhu4-1 子电路。

- 4) 移动光标到新的原理图设计窗口中，就可以在绘图区插入 zhuanzhu4-1 子电路了。

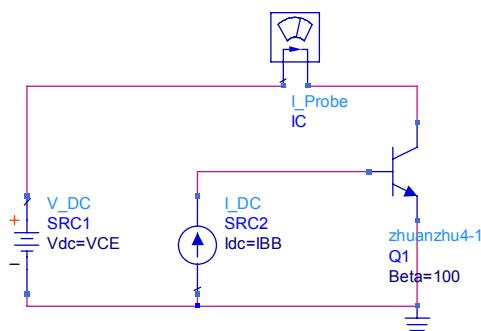

- (5) 创建直流仿真电路原理图

电路符号创建完毕，就可以创建直流仿真电路原理图了。

- 1) 在 Sources-Freq Domain 列表中选择直流电压源 V\_DC，并插入到原理图中。双击 V\_DC，在弹出的参数设置对话框中将 Vdc 的值设置为 VCE，单击 OK 按钮确定。

- 2) 在 Sources-Freq Domain 列表中选择直流电流源 I\_DC，并插入到原理图中。双击 I\_DC，在弹出的参数设置对话框中将 Idc 的值设置为 IBB，单击 OK 按钮确定。

- 3) 在 Probe Components 列表中选择电流观察仪器 I\_Probe，将它放在合适的位置上。

- 4) 将所有插入的元件按照图 4-13 所示的方式连接起来。

图 4-13 直流仿真原理电路图

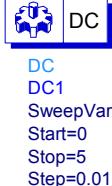

- 5) 在 Simulation-DC 列表中选择直流仿真器 DC，并放置在原理图窗口中。双击直流仿真器，按照下面的内容进行修改：

- ① 设置 Parameter to sweep 为 VCE。

- ② 设置 Sweep Type 为 Linear。

- ③ Start=0，表示扫描变量 VCE 的起始值为 0。

- ④ Stop=5，表示扫描变量 VCE 的终止值为 5。

- ⑤ Step-size=0.01，表示扫描变量 VCE 的扫描间隔为 0.01。

设置完成后，单击 OK 按钮完成设置，如图 4-14 所示。

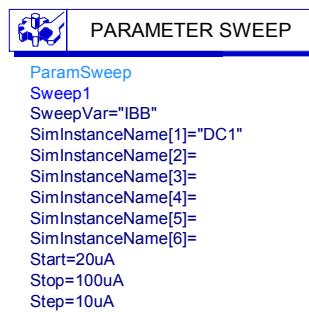

6) 在 Simulation-DC 列表中选择 PrmSwp。

- ①设置 Parameter to sweep 为 IBB，表示扫描参数为 IBB。

- ②设置 Sweep Type 为 Linear，表示扫描类型为线性扫描。

- ③Start=20uA，表示扫描变量 IBB 的起始值为 20uA（注意：用 uA 表示微安）。

- ④Stop=100uA，表示扫描变量 IBB 的终止值为 100uA。

- ⑤Step-size=10uA，表示扫描变量 IBB 的扫描间隔为 10uA。

然后，选择 Simulation 选项卡，在 Simulation1 中添入 DC1，表示扫描是针对 DC1 进行仿真的。

单击 OK 按钮完成设置，如图 4-15 所示。

图 4-14 设置直流仿真器

图 4-15 设置参数扫描控件

7) 在 Simulation-DC 列表中选择显示模板控件 Disp Temp，并放置在原理图设计窗口中。双击 Disp Temp，在弹出的 Automatic Data Display Template 窗口中设置仿真结果的显示模板。

- ①单击 Browse installed templates 按钮。

②在弹出的 Component Library/Template Browsers 窗口的左窗格中先选择 product 文件夹，在右窗格中选择 BJT\_curve\_tracer 元件。

③最后回到 Automatic Data Display Template 窗口中单击 Add 按钮添加模板，并单击 OK 按钮确定。

完成设置的显示模板控件如图 4-16 所示。

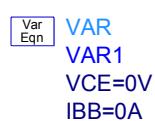

8) 单击工具栏中的 VAR 按钮，在原理图中插入一个变量控件，双击变量控件，按下面的内容进行参数设置：

- ①VCE=0V，表示 VCE 为变量，且默认值为 0V。

- ②IBB=0A，表示 IBB 为变量，且默认值为 0A。

设置完成后单击 OK 按钮确认，完成设置的变量控件如图 4-17 所示。

图 4-16 设置显示模板控件

图 4-17 变量控件

## 2. 原理图仿真

(1) 在工具栏中单击 Simulate 按钮执行仿真，由于在原理图中加入了数据显示模板，因此仿真数据会与绘图结果一起生成。

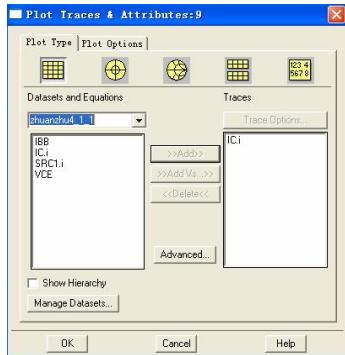

(2) 在列表框中插入 IC.i 数据，注意 VCE 数据是缺省的 X 轴数据，不必插入，如图 4-18 所示。

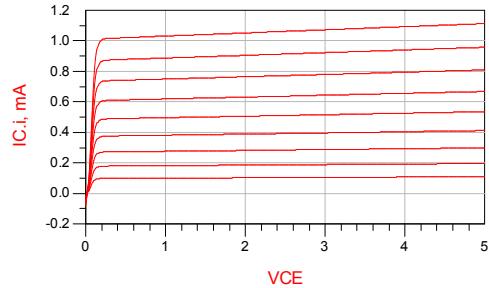

(3) 观察数据窗口，此时窗口出现了关于 IC 与 VCE 的数据曲线，如图 4-19 所示。

图 4-18 插入 IC.i 数据

图 4-19 仿真结果

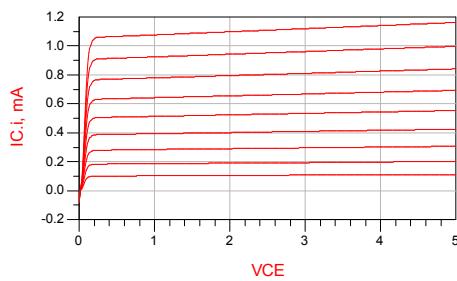

(4) 在原理图中改变 Beta=140，重新仿真，新的 IC 与 VCE 的数据曲线如图 4-20 所示。

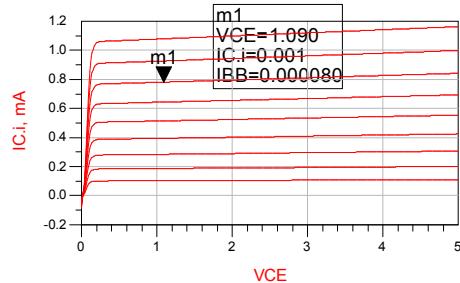

(5) 在曲线上插入一个新的 Marker，可以看到不同点处的具体参数值，如图 4-21 所示。

图 4-20 Beta=140 时的仿真结果

图 4-21 插入一个 Marker，显示具体参数

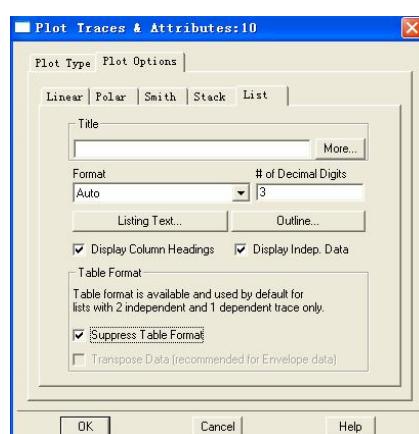

(6) 插入 list 按钮 ，插入 IC.i 数据，如果出现如图 4-22 所示的图形，双击该图形，单击 Plot Options 选项卡，选中 Suppress Table Format 复选框（见图 4-23），就可以显示正确的数据，如图 4-24 所示。

图 4-22 显示数据错误

图 4-23 选择 Suppress Table Format

| VCE                       | IC.i     |

|---------------------------|----------|

| I <sub>BB</sub> =2.000E-5 | -14.62uA |

| 0.000                     | -7.112uA |

| 0.020                     | 1.956uA  |

| 0.030                     | 12.48uA  |

| 0.040                     | 24.14uA  |

| 0.050                     | 36.38uA  |

| 0.060                     | 48.47uA  |

| 0.070                     | 59.72uA  |

| 0.080                     | 69.56uA  |

| 0.090                     | 77.70uA  |

| 0.100                     | 84.12uA  |

| 0.110                     | 89.00uA  |

| 0.120                     | 92.58uA  |

| 0.130                     | 95.16uA  |

| 0.140                     | 96.98uA  |

| 0.150                     | 98.26uA  |

| 0.160                     | 99.15uA  |

| 0.170                     | 99.76uA  |

| 0.180                     | 100.2uA  |

| 0.190                     | 100.5uA  |

| 0.200                     | 100.7uA  |

| 0.210                     | 100.8uA  |

| 0.220                     | 101.0uA  |

| 0.230                     | 101.0uA  |

| 0.240                     | 101.1uA  |

| 0.250                     | 101.1uA  |

| 0.260                     | 101.2uA  |

| 0.270                     | 101.2uA  |

| 0.280                     | 101.2uA  |

| 0.290                     | 101.3uA  |

图 4-24 显示 IC.i 数据

## 4.2 元器件的等效电路模拟

### 4.2.1 示波器探针的等效电路模型

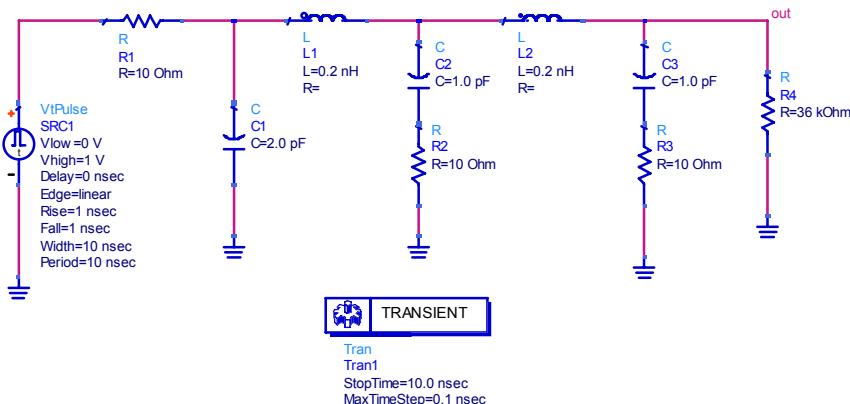

本节建立一个示波器探针的电路模型，各个元器件的参数如图 4-25 所示。

图 4-25 示波器探针的等效电路模型

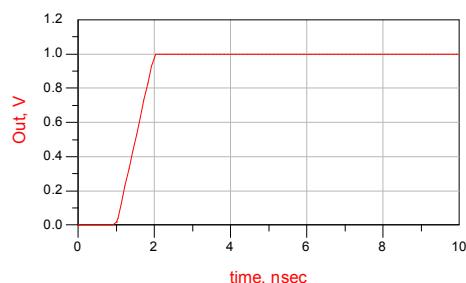

仿真的电压测试点的波形如图 4-26 所示。

图 4-26 电压测试点的波形

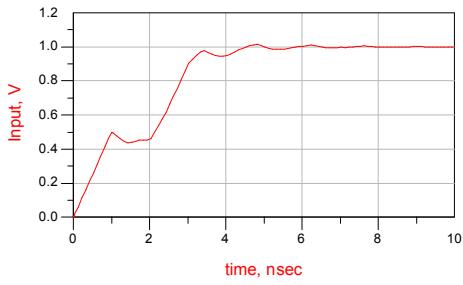

如果电感减小为 0.2nH, 如图 4-27 所示, 那么仿真效果如图 4-28 所示。

图 4-27 电感减小为 0.2nH

图 4-28 电感为 0.2nH 时的仿真结果

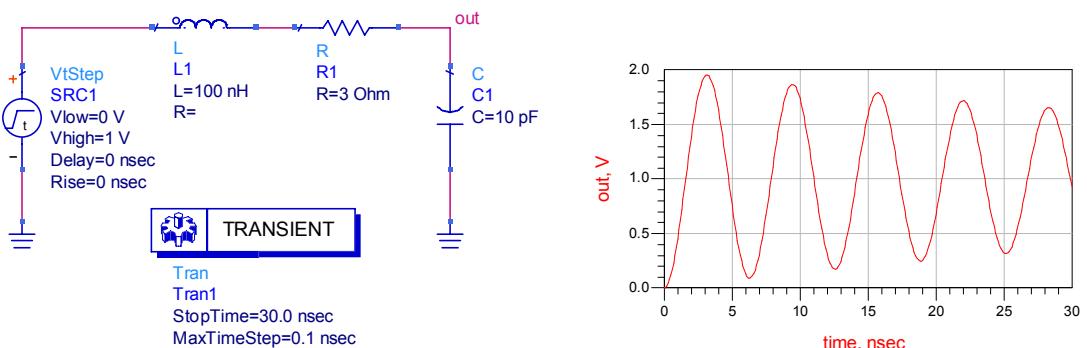

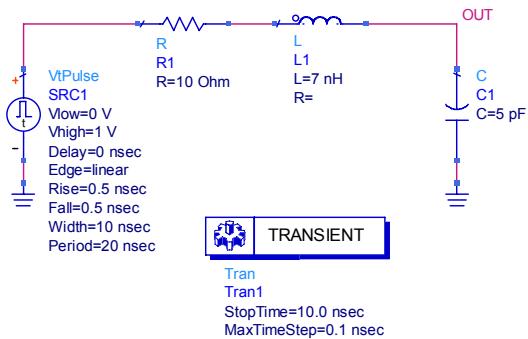

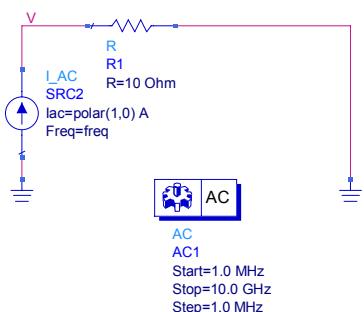

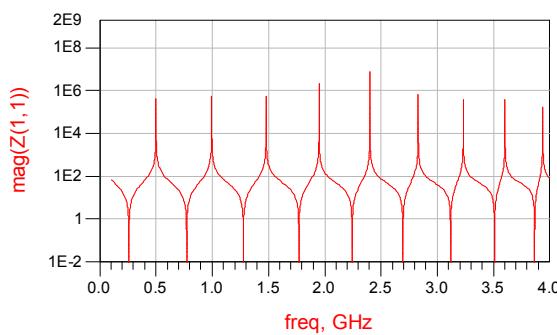

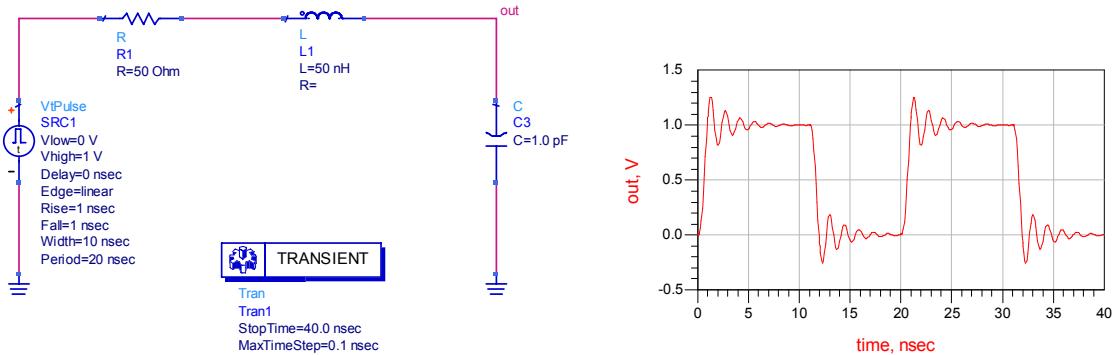

#### 4.2.2 RLC 电路的时域行为

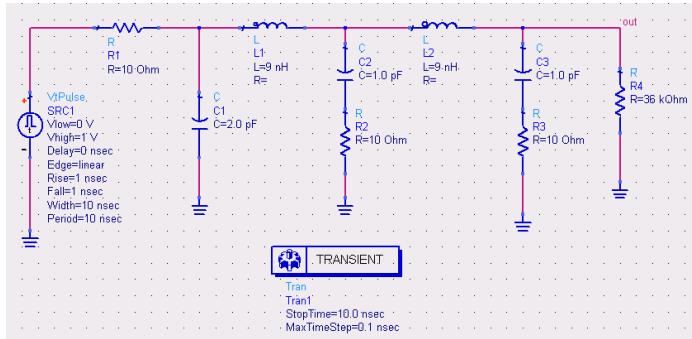

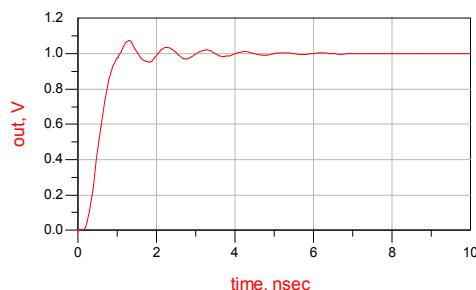

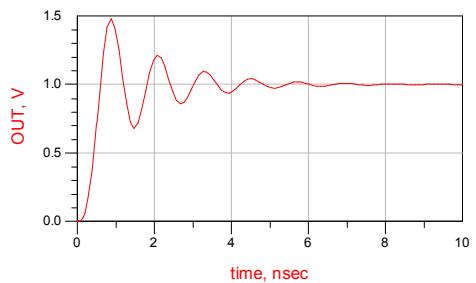

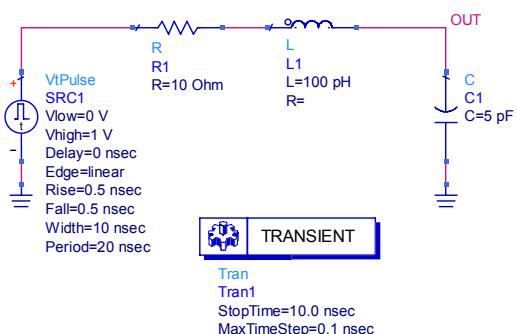

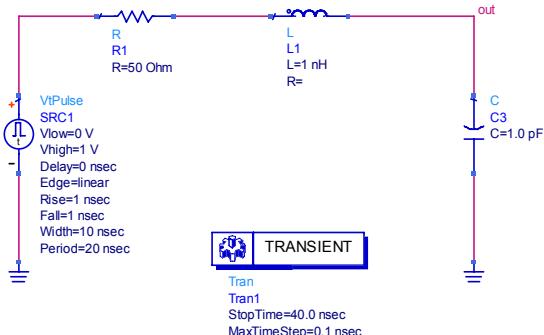

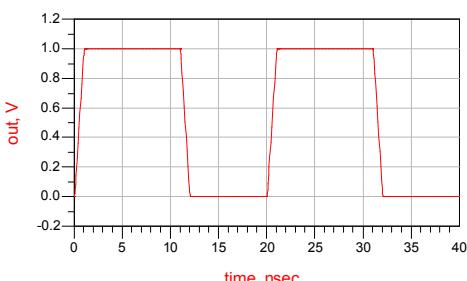

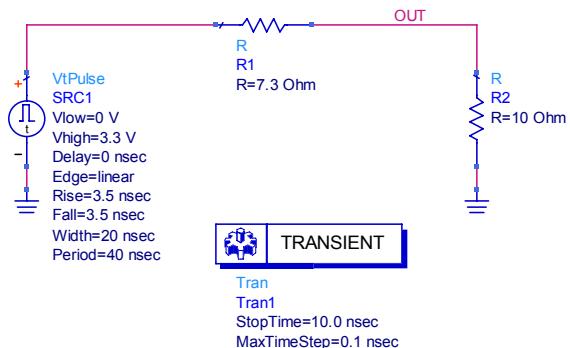

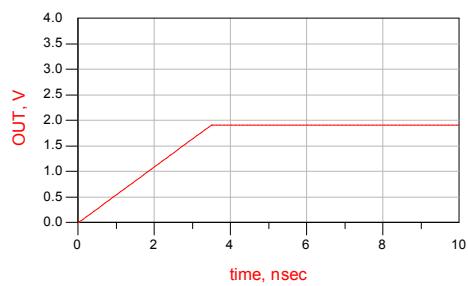

为了观察 RLC 电路的时域行为, 建立了如图 4-29 所示的电路模型, 从仿真结果(见图 4-30)可以看到, 当数字信号与互连线(它常常可以描述成理想 RLC 电路元件的组合)相互作用时, 就产生正弦波。

图 4-29 RLC 电路

图 4-30 RLC 电路产生的正弦波

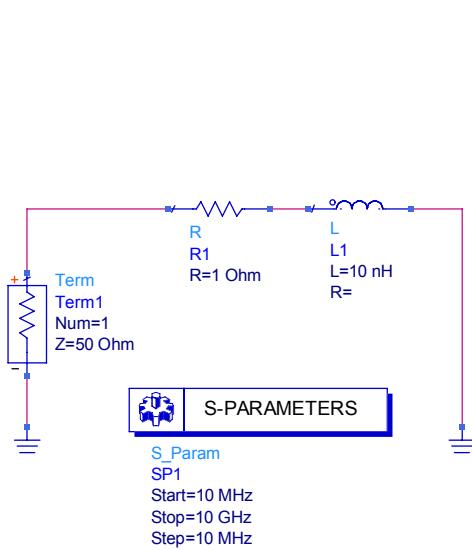

### 4.2.3 两焊盘间键合线回路的等效电路模型

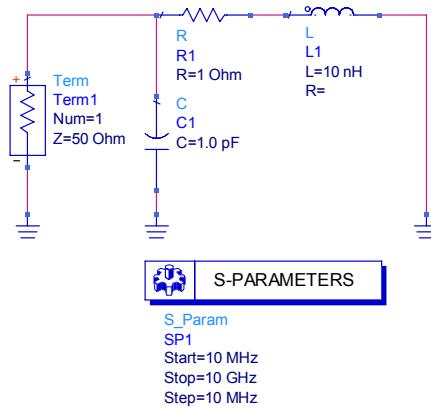

本节仿真两焊盘间键合线回路的等效电路模型。

(1) 一阶模型如图 4-31 所示。

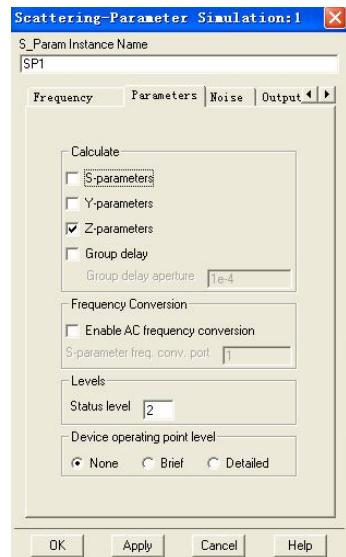

(2) 双击仿真器 S-PARAMETERS，在 Parameters 中选择 Z-parameters，如图 4-32 所示。

图 4-31 两焊盘间键合线回路的一阶等效电路模型

图 4-32 选择 Z-parameters

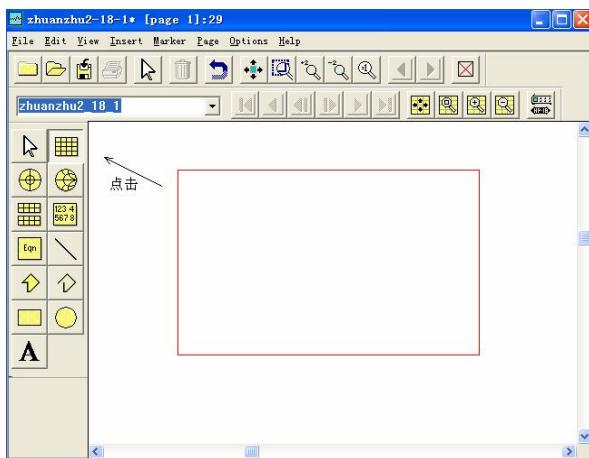

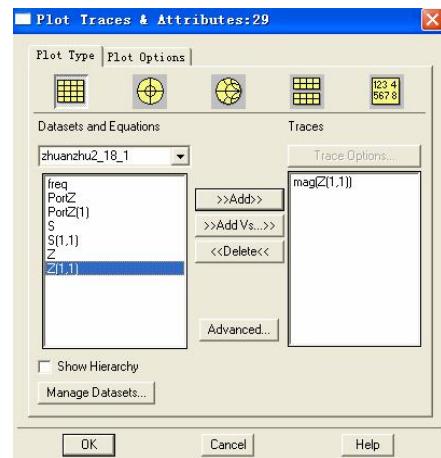

(3) 仿真结束后，单击画图按钮，出现红色画图框，如图 4-33 所示。在 Plot Type 选项卡中选择要画的项，添加到右边的栏中，如图 4-34 所示。选择 Plot Options 选项卡，选择 X Axis，在 Min 中填入 1e7，在 Scale 中选择 Log 坐标，如图 4-35 所示。

图 4-33 单击画图按钮

图 4-34 插入 Z(1,1)

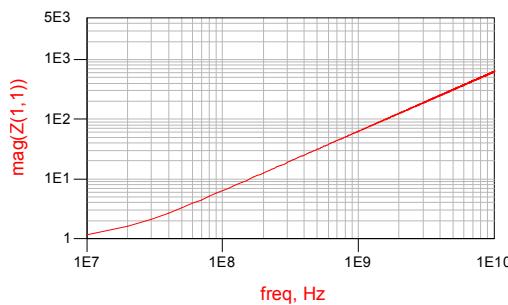

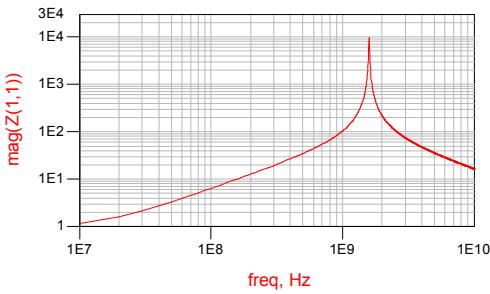

选择 Y Axis，在 Min 中填入 1，在 Max 中填入 5e3，在 Scale 中选择 Log 坐标，如图 4-36 所示。阻抗结果如图 4-37 所示。

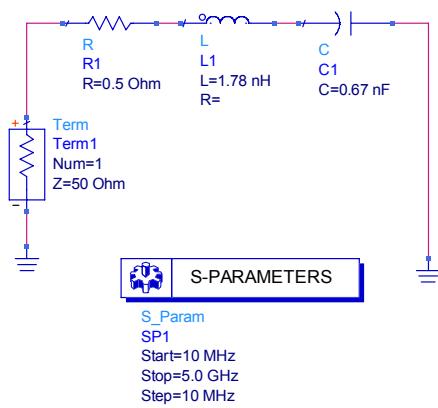

(4) 二阶模型如图 4-38 所示。

图 4-35 选择 X 轴 Log

图 4-36 选择 Y 轴 Log

图 4-37 阻抗随频率的变化曲线

图 4-38 两焊盘间键合线回路的二阶等效电路模型

X 和 Y 轴的尺度改变如图 4-39 和图 4-40 所示。阻抗仿真结果如图 4-41 所示。

图 4-39 选择 X 轴 Log

图 4-40 选择 Y 轴 Log

图 4-41 二阶模型时阻抗随频率的变化曲线

#### 4.2.4 去耦电容的等效电路模型

(1) 本节仿真去耦电容的等效电路模型, 图 4-42 是用 ADS 建立的等效电路模型。

(2) 在图形中选择 Plot Options 选项卡, 选择 X Axis, 在 Min 中填入 1e7, 在 Scale 中选择 Log 坐标, 如图 4-43 和图 4-44 所示。

图 4-42 去耦电容的等效电路模型

图 4-43 Plot Options 选项卡 X 轴

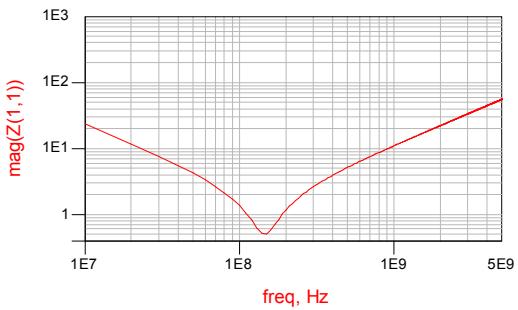

(3) 阻抗仿真结果如图 4-45 所示。

图 4-44 Plot Options 选项卡 Y 轴

图 4-45 阻抗仿真结果

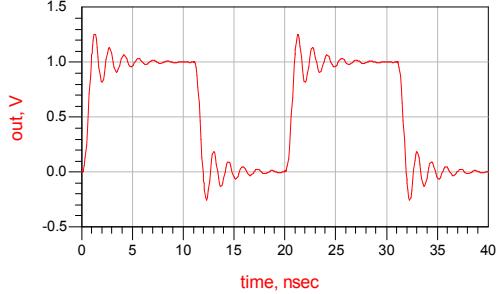

#### 4.2.5 驱动器的等效电路模型

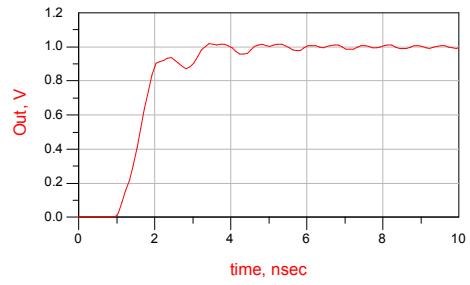

本节仿真驱动器的等效电路模型，电路图如图 4-46 所示。

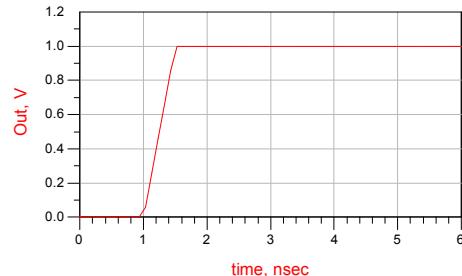

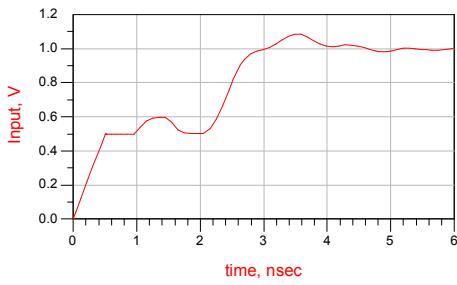

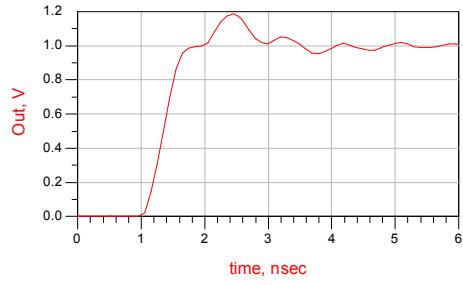

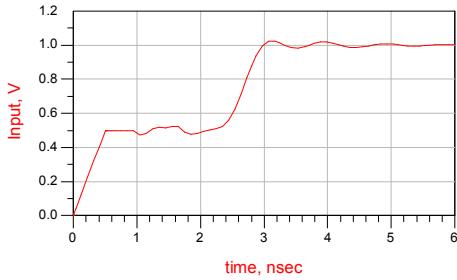

仿真结果如图 4-47 所示。

图 4-46 驱动器的等效电路

图 4-47 驱动器的仿真结果

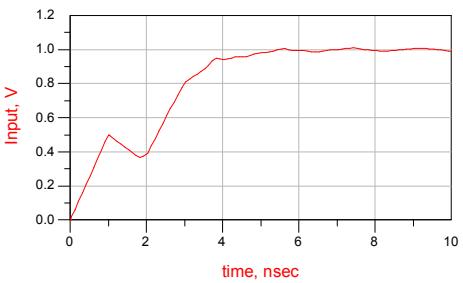

如果减少电感（见图 4-48），振铃就将消失（见图 4-49）。

图 4-48 减小电感后的电路

图 4-49 减小电感后的仿真结果

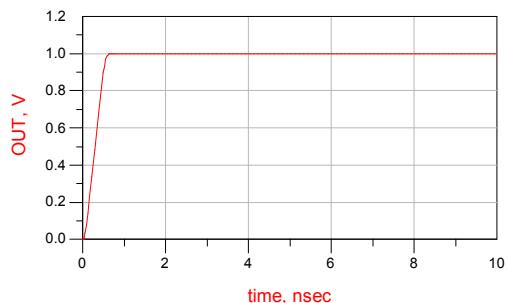

#### 4.2.6 如何构造求阻抗的电路模型

本节介绍如何构造求阻抗的电路模型。方法是：构造一个幅度为 1A 的交流恒流源，测量电流源两端的电压就是对这个电路的阻抗的直接测量。例如，只有一个电阻的情况如图 4-50 所示。仿真结果如图 4-51 所示。

图 4-50 只有一个电阻的情况

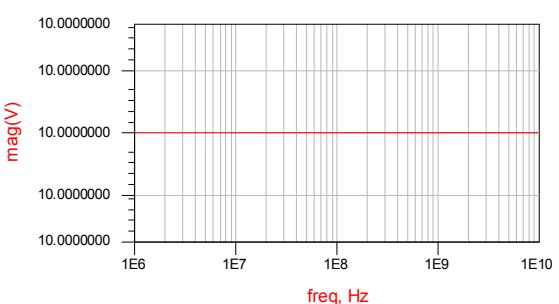

图 4-51 只有一个电阻的仿真结果

只有一个电感的情况如图 4-52 所示，仿真结果如图 4-53 所示。

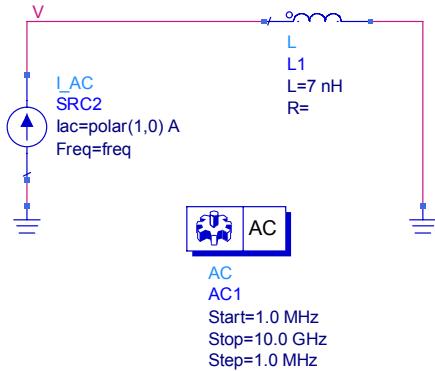

图 4-52 只有一个电感的情况

图 4-53 只有一个电感的仿真结果

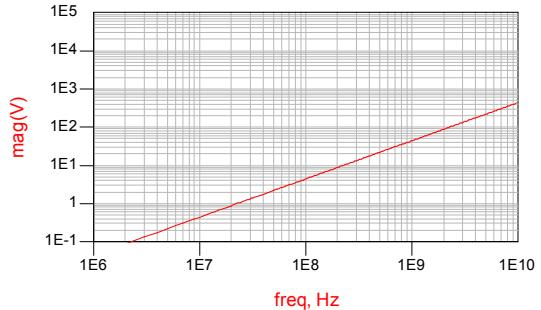

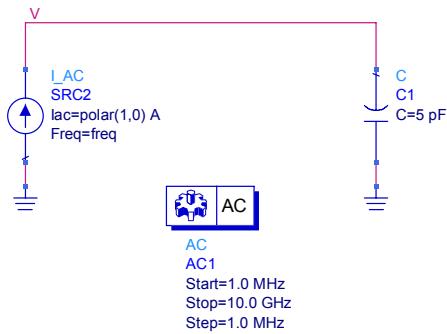

只有一个电容的情况如图 4-54 所示，仿真结果如图 4-55 所示。

图 4-54 只有一个电容的情况

图 4-55 只有一个电容的仿真结果

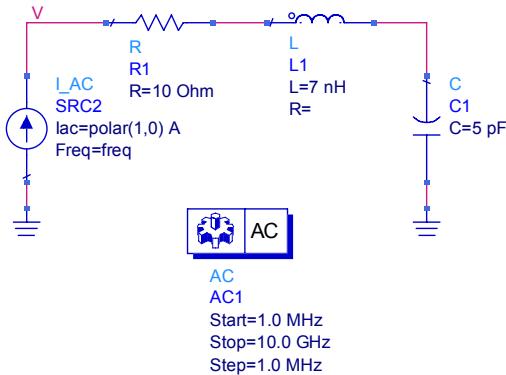

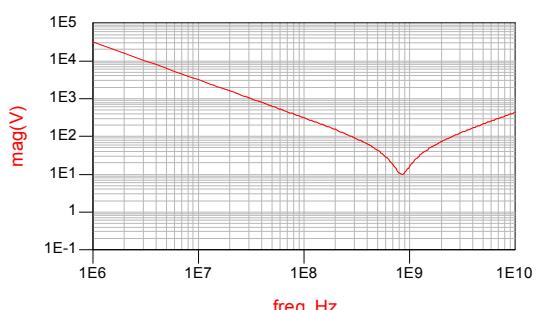

电阻、电感、电容串联的情况如图 4-56 所示。

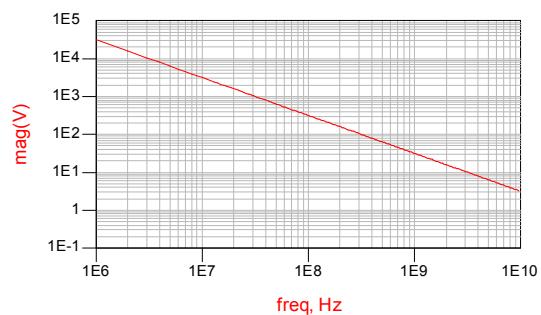

幅度仿真结果如图 4-57 所示。

图 4-56 电阻、电感、电容串联的情况

图 4-57 电阻、电感、电容串联的幅度仿真结果

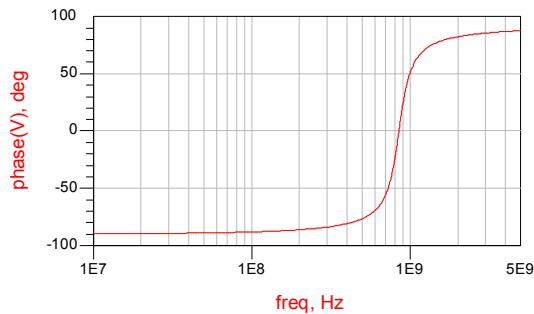

相位仿真结果如图 4-58 所示。

图 4-58 电阻、电感、电容串联的相位仿真结果

#### 4.2.7 传输线的等效电路模型

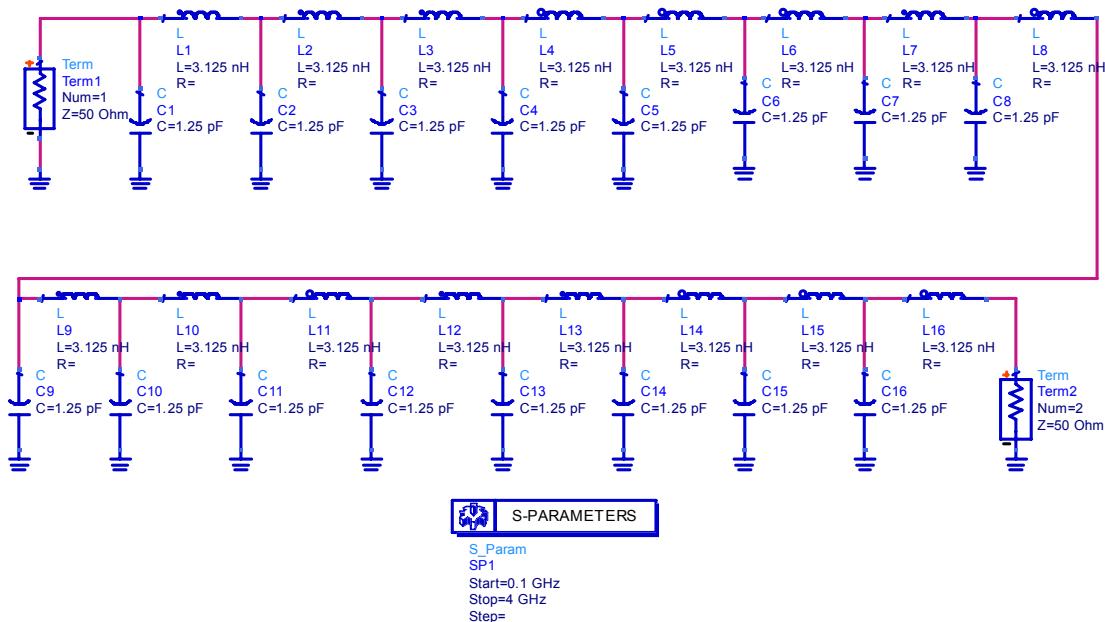

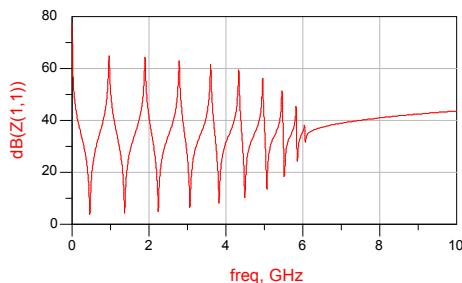

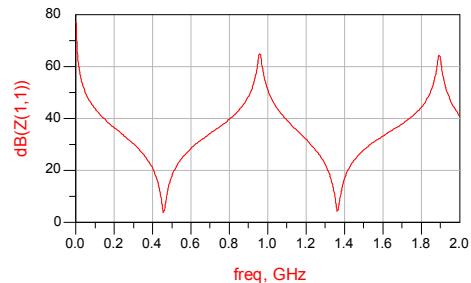

16 节 LC 集总电路模型如图 4-59 所示。仿真的阻抗特性曲线如图 4-60 所示。

图 4-59 16 节 LC 集总电路模型

图 4-60 16 节 LC 集总电路模型的仿真阻抗

## 4.3 传输线的反射仿真

### 4.3.1 阻抗不匹配而产生的振铃

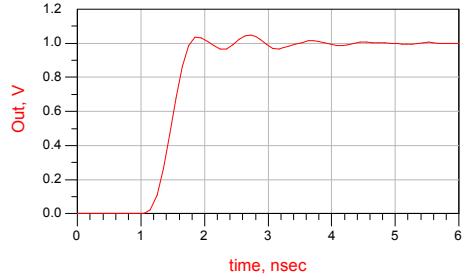

图 4-61 所示为输出端阻抗不匹配的情况，输出端的仿真结果如图 4-62 所示，由图可见，波形产生了振铃。

图 4-61 输出端阻抗不匹配的情况

图 4-62 输出端产生了振铃

图 4-63 为输出端匹配的情况，仿真结果如图 4-64 所示，由图可见，振铃消失了。

图 4-63 输出端匹配的情况

图 4-64 输出端振铃消失了

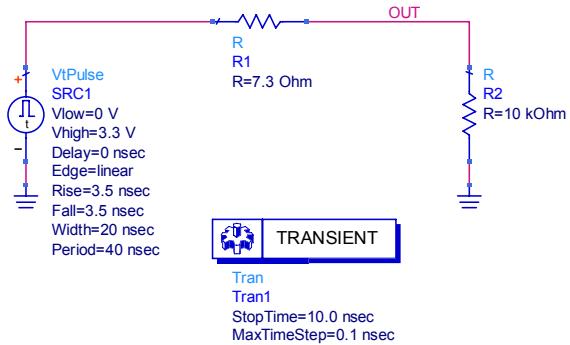

### 4.3.2 驱动源的内阻抗情况

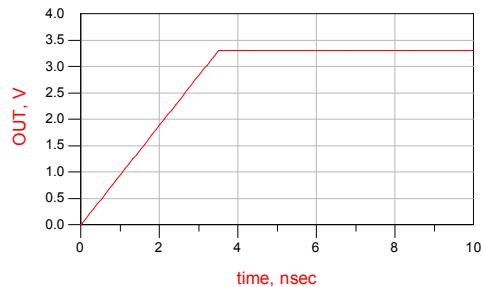

图 4-65 所示为输出驱动器的简单模型，要观察输出开路和驱动  $10\Omega$  电阻的仿真结果。根据测

量结果来计算驱动源的内阻。驱动器输出开路模型如图 4-65 所示，仿真结果如图 4-66 所示。

图 4-65 驱动器输出开路的模型

图 4-66 驱动器输出开路仿真结果

驱动器输出接  $10\Omega$  电阻的电路模型如图 4-67 所示，仿真结果如图 4-68 所示。

图 4-67 驱动器输出接  $10\Omega$  电阻的电路模型

图 4-68 驱动器输出接  $10\Omega$  电阻的仿真结果

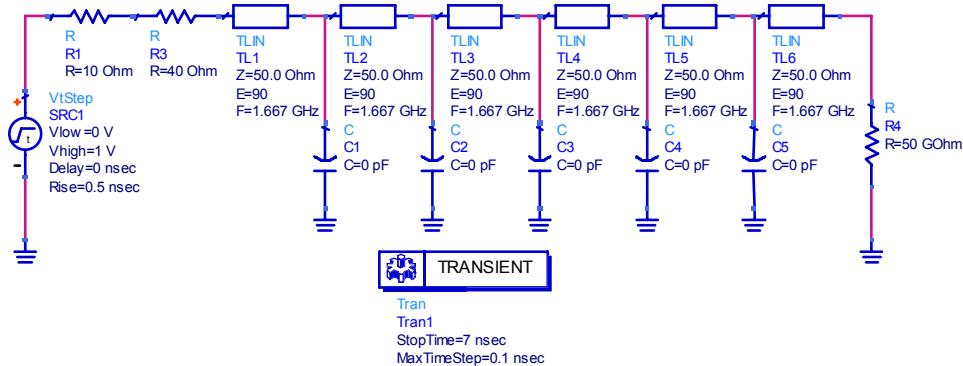

### 4.3.3 反弹图仿真

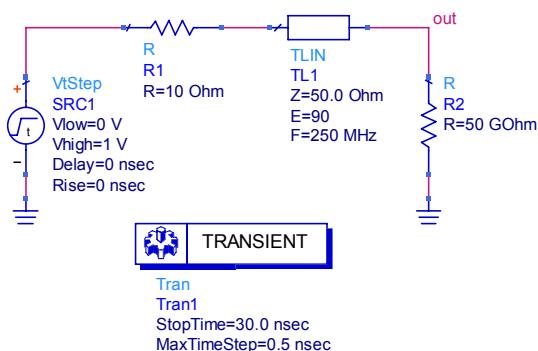

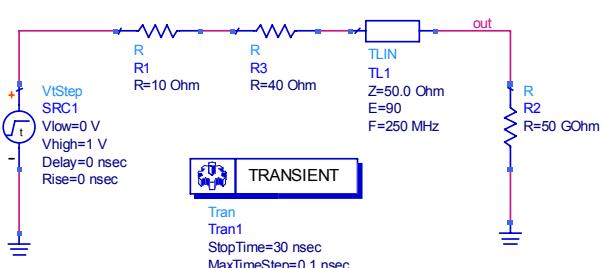

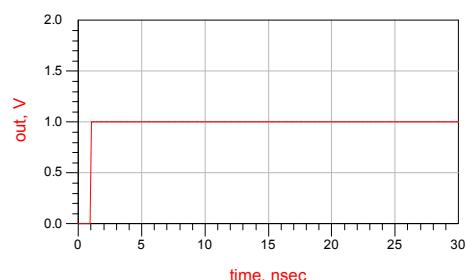

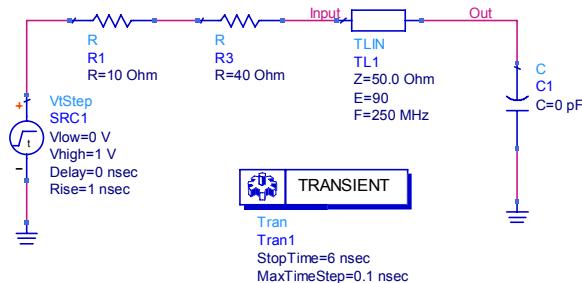

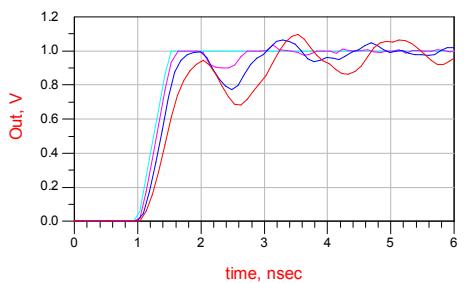

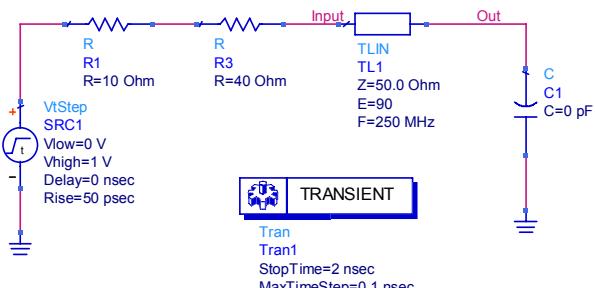

本节建立反弹图的模型并仿真。如何从图 8.9 中的参数转换成 ADS 中的参数？在图 8.9 中， $1ns \times 3e8 = 0.3m$ ，对应 ADS 中， $\lambda = 4 \times 0.3 = 1.2m$ （电尺寸  $E=90^\circ$ ，即  $1/4$  波长），所以  $f = 3e8 / 1.2 = 250MHz$ 。电路原理图如图 4-69 所示。

图 4-69 反弹图电路模型

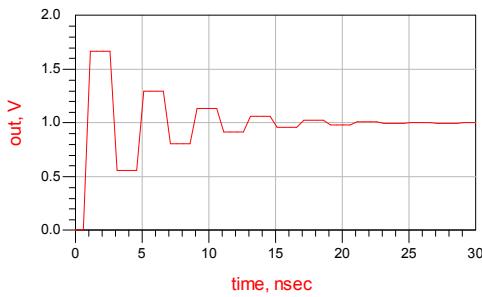

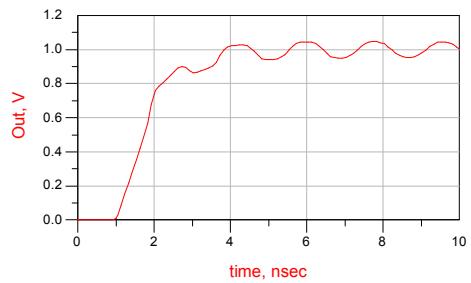

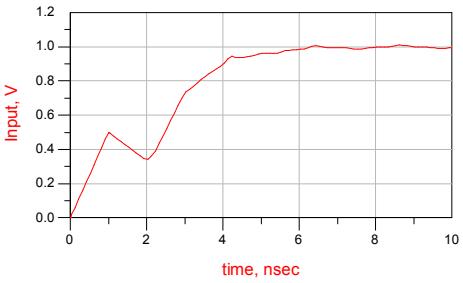

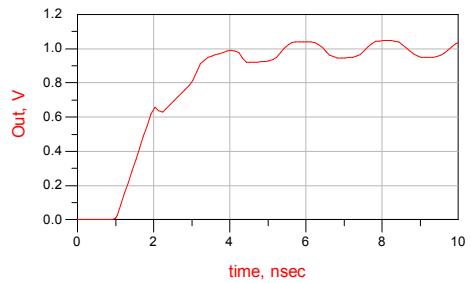

仿真结果如图 4-70 所示。

图 4-70 反弹图仿真结果

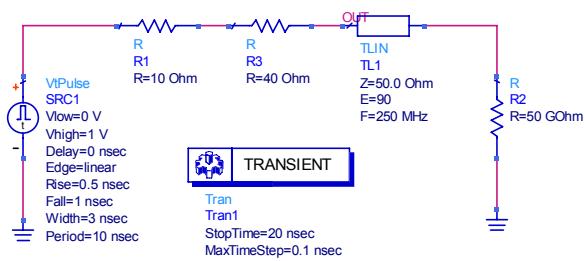

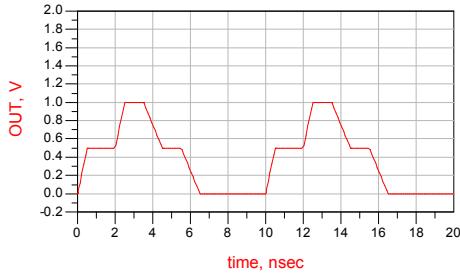

#### 4.3.4 反射波形仿真

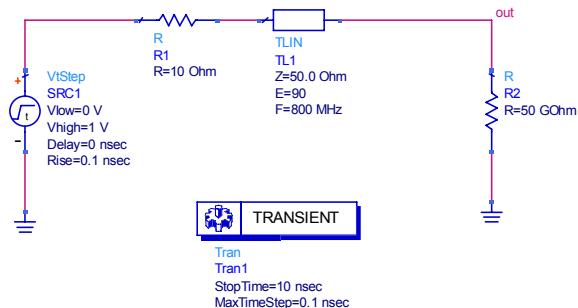

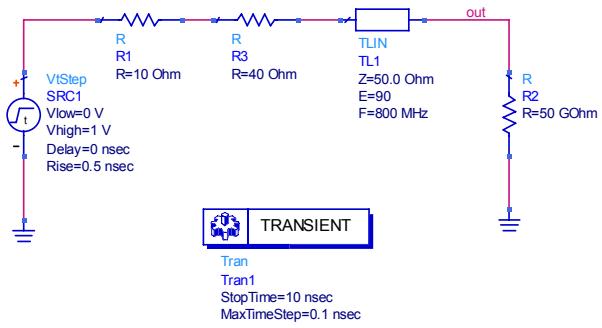

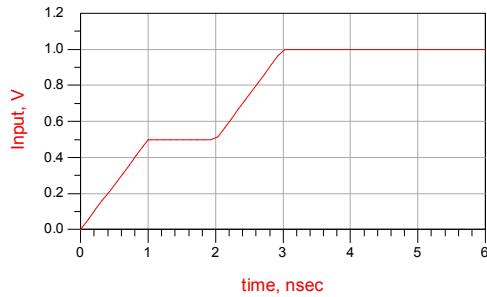

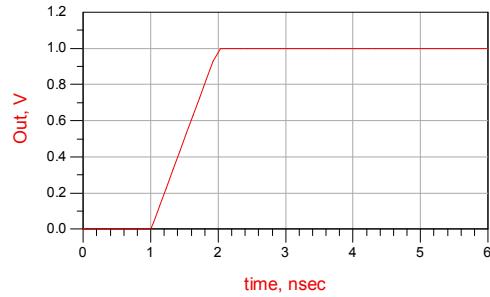

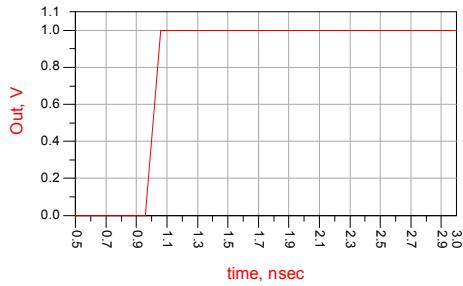

原理图见图 4-71。传输线频率 800MHz，改变信号上升时间从 0.1ns 到 1.5ns，仿真结果分别如图 4-72、图 4-73 和图 4-74 所示。

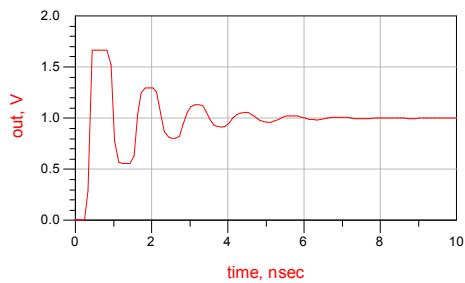

上升时间为 0.1ns 时的仿真结果如图 4-72 所示。

图 4-71 反射波形仿真原理图

图 4-72 上升时间为 0.1ns 时的仿真结果

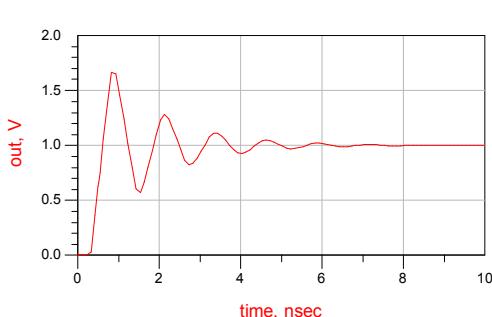

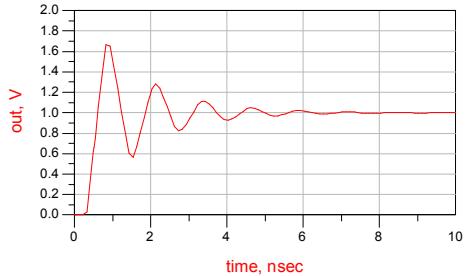

上升时间为 0.5ns 时的仿真结果如图 4-73 所示。

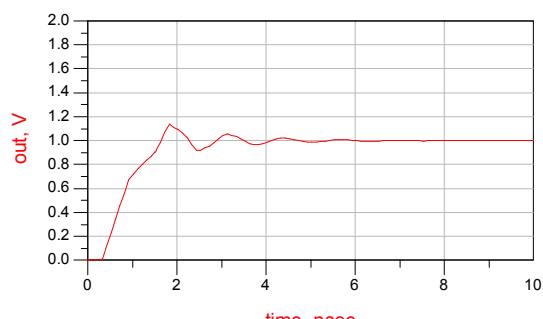

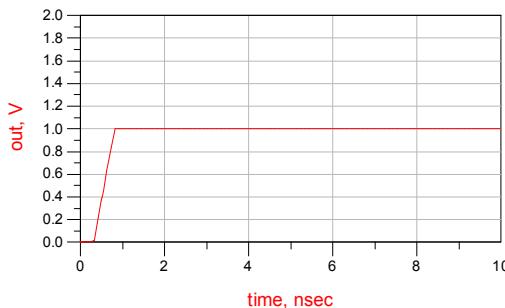

上升时间为 1.5ns 时的仿真结果如图 4-74 所示。

图 4-73 上升时间为 0.5ns 时的仿真结果

图 4-74 上升时间为 1.5ns 时的仿真结果

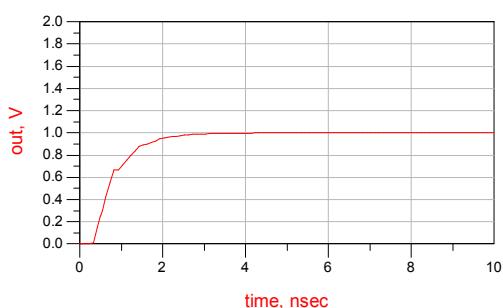

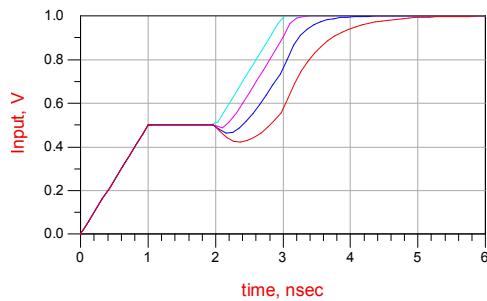

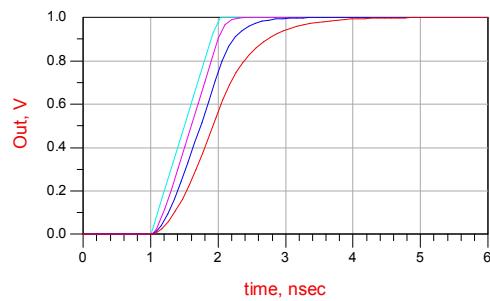

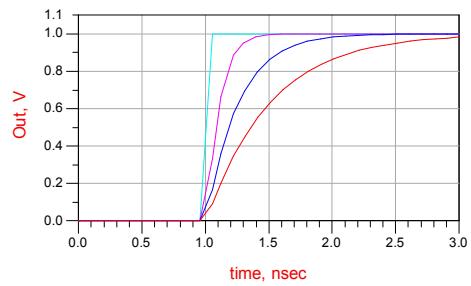

上升时间改为 0.5ns，源端串联电阻 R，原理图如图 4-75 所示，当 R=0Ω、40Ω、90Ω 时的仿真结果分别如图 4-76、图 4-77 和图 4-78 所示。

当  $R=0\Omega$  时的结果如图 4-76 所示。

图 4-75 原理图

图 4-76  $R=0\Omega$  时的仿真结果

当  $R=40\Omega$  时的结果如图 4-77 所示。

当  $R=90\Omega$  时的结果如图 4-78 所示。

图 4-77  $R=40\Omega$  时的仿真结果图 4-78  $R=90\Omega$  时的仿真结果

### 4.3.5 仿真 TDR 测量原理

本节仿真 TDR 测量原理。

(1) DUT 匹配情况：原理图如图 4-79 所示，仿真结果如图 4-80 所示。

图 4-79 DUT 匹配情况原理图

图 4-80 DUT 匹配情况仿真结果

(2) DUT 开路情况：原理图如图 4-81 所示，仿真结果如图 4-82 所示。

图 4-81 DUT 开路情况原理图

图 4-82 DUT 开路情况仿真结果

(3) DUT 短路情况: 原理图如图 4-83 所示, 仿真结果如图 4-84 所示。

图 4-83 DUT 短路情况原理图

图 4-84 DUT 短路情况仿真结果

#### 4.3.6 何时需要端接

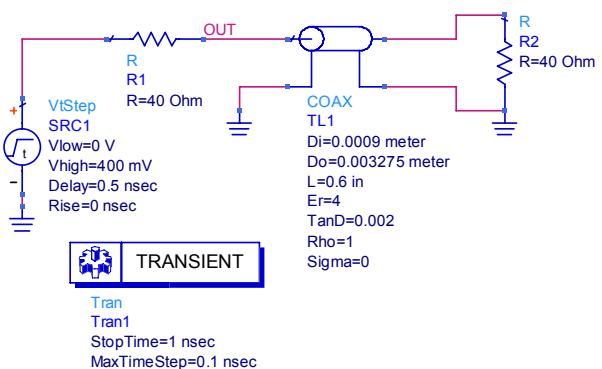

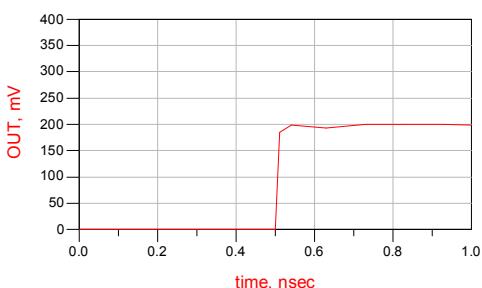

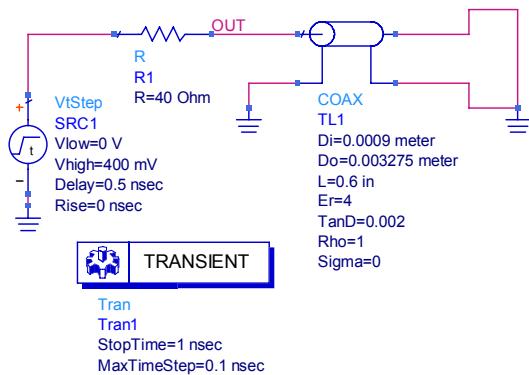

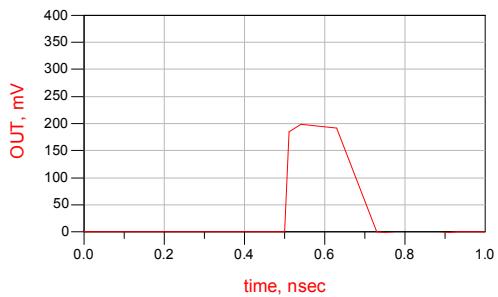

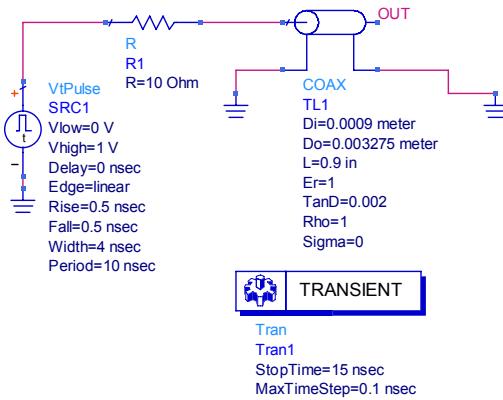

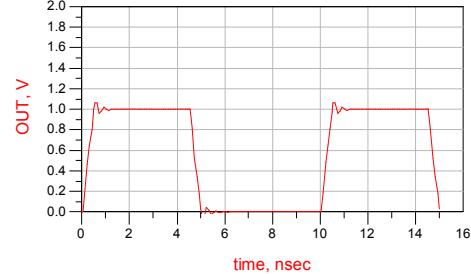

当  $RT=0.5\text{ns}$  时,  $TD=20\%RT=0.6\text{in}$  的原理图和仿真结果如图 4-85 和图 4-86 所示。

图 4-85 TD=0.6in 时的电路图

图 4-86 TD=0.6in 时的仿真结果

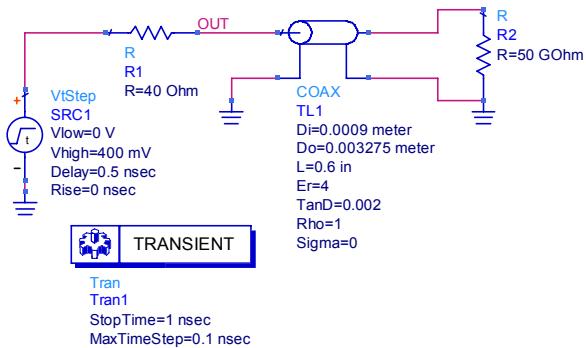

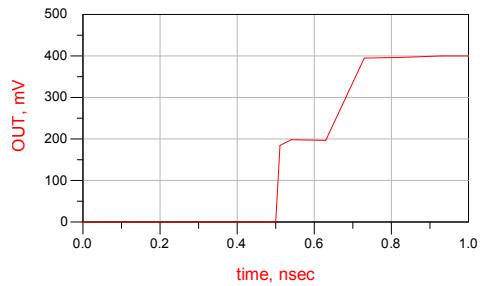

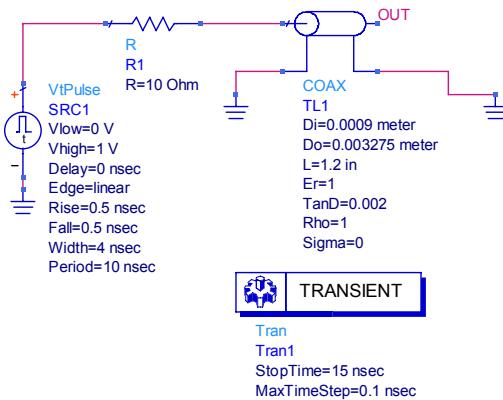

$TD=30\%RT=0.9\text{in}$  的原理图和仿真结果如图 4-87 和图 4-88 所示。

图 4-87 TD=0.9in 时的原理图

图 4-88 TD=0.9in 时的仿真结果

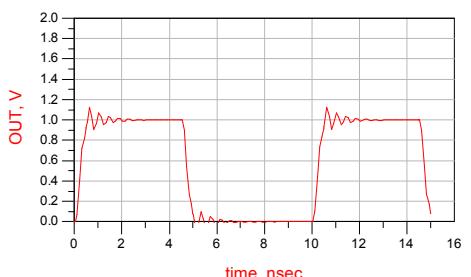

TD =40%RT=1.2in 的原理图和仿真结果如图 4-89 和图 4-90 所示。

图 4-89 TD=1.2in 时的原理图

图 4-90 TD=1.2in 时的仿真结果

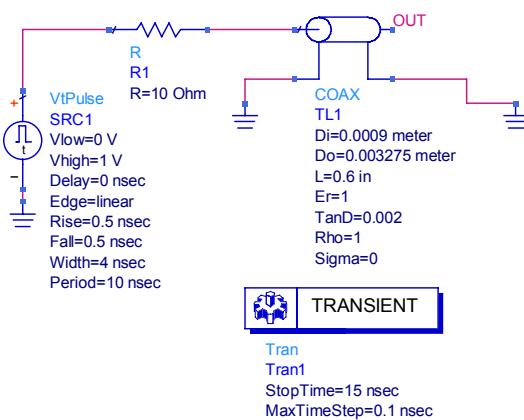

### 4.3.7 源端端接

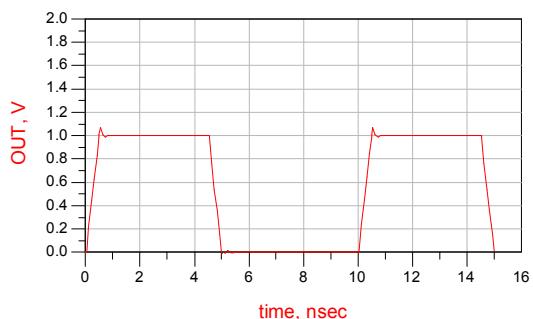

源端端接, 如图 4-91 所示, 仿真结果如图 4-92 所示。

图 4-91 源端端接图

图 4-92 源端端接的仿真结果

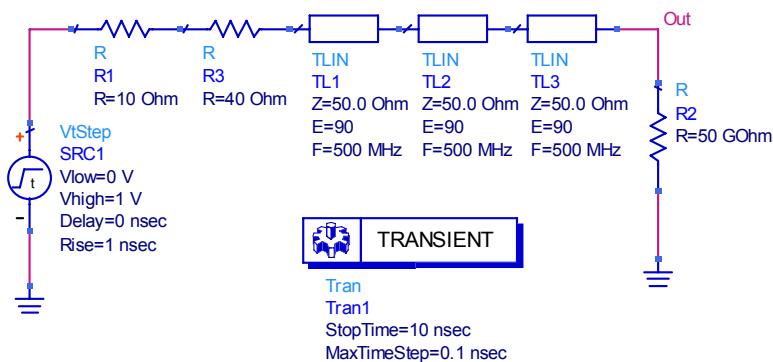

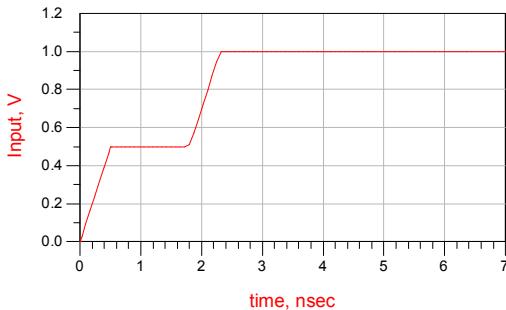

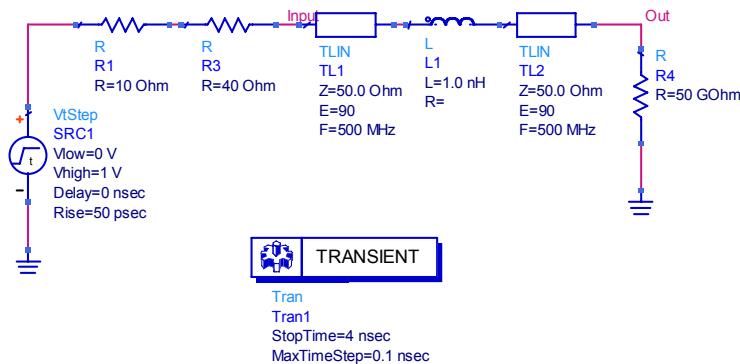

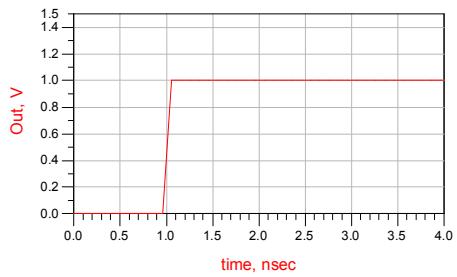

### 4.3.8 源端端接情况下的传输线增加

光速=0.3m/ns=12in/ns, 1ns 传输线长度对应 0.3m, 对应传输线频率 F=250MHz。

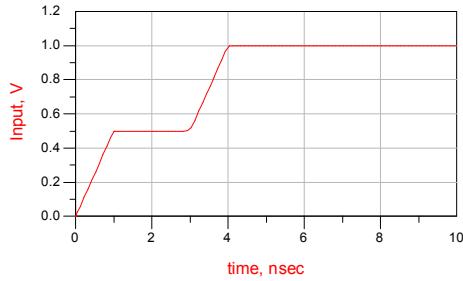

计算方法：根据传输线参数，传输线长度= $v/(F/4) = 0.3/(0.25/4) = 0.3$ 。因此图 4-93 满足  $2 \times TD = 2$ ns。仿真结果如图 4-94 所示。

图 4-93 原理图

图 4-94 满足  $2 \times TD = 2$ ns 的仿真结果

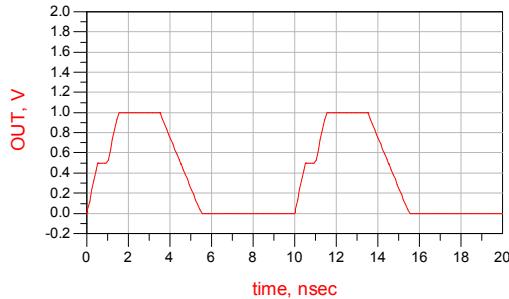

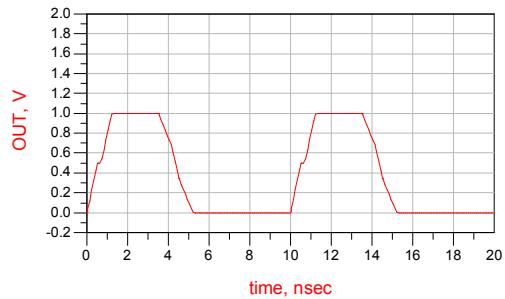

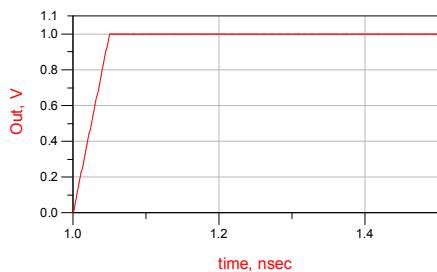

传输线频率改为  $F=500MHz$ , 传输线长度= $0.5ns$ , 仿真结果如图 4-95 所示。

传输线频率改为  $F=714MHz$ , 传输线长度= $0.35ns$ , 仿真结果如图 4-96 所示。

图 4-95 满足  $2 \times TD = 1$ ns 的仿真结果图 4-96 满足  $2 \times TD = 0.7$ ns 的仿真结果

#### 4.3.9 短串接传输线的反射

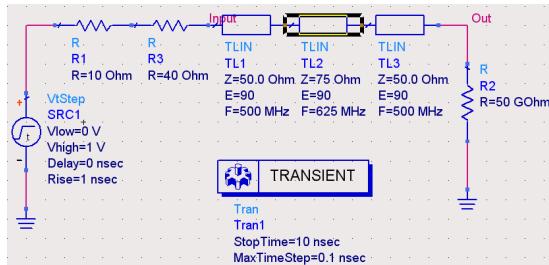

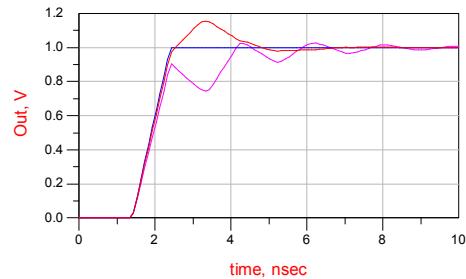

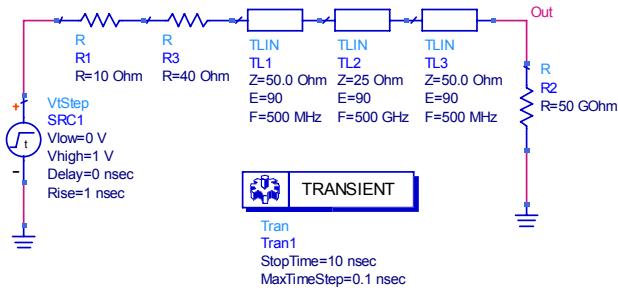

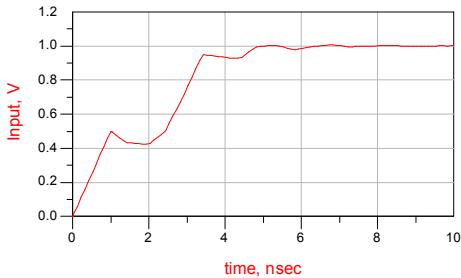

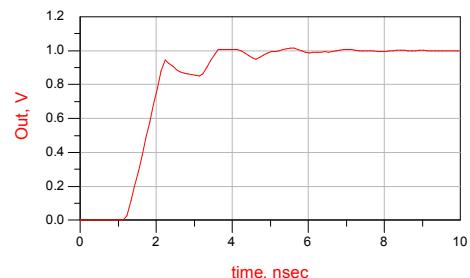

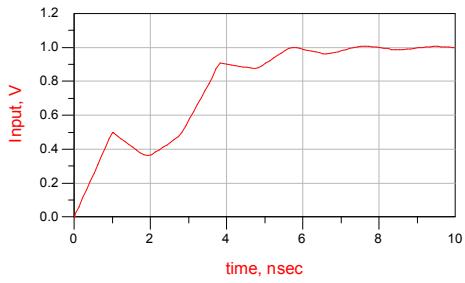

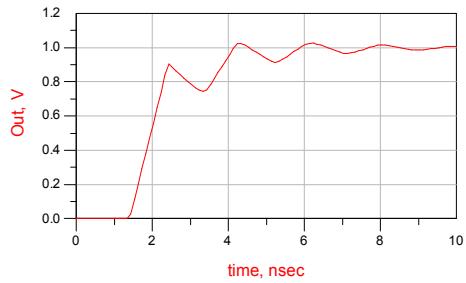

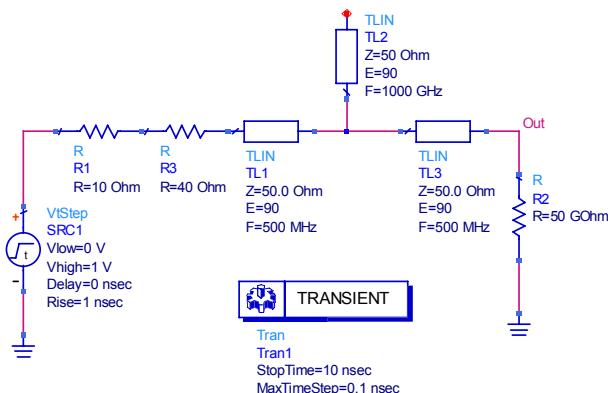

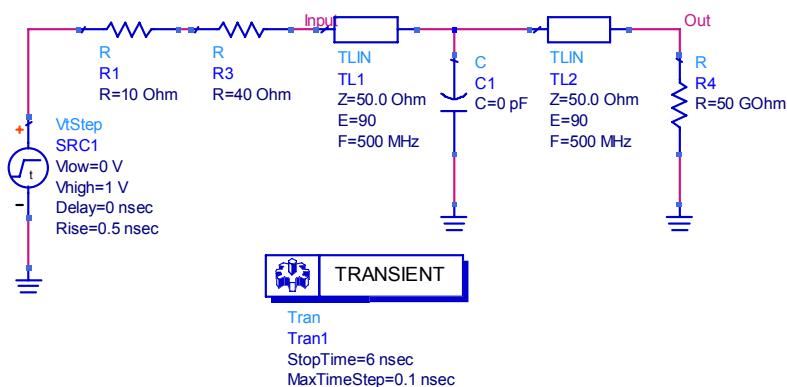

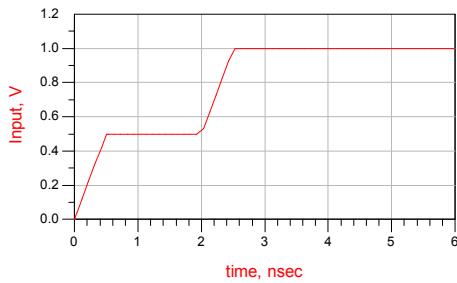

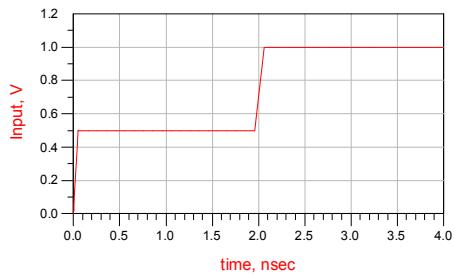

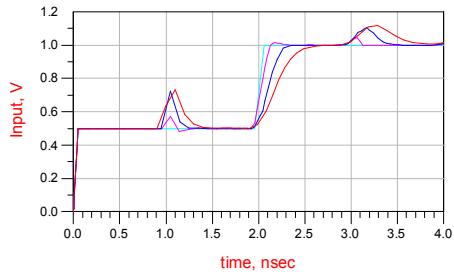

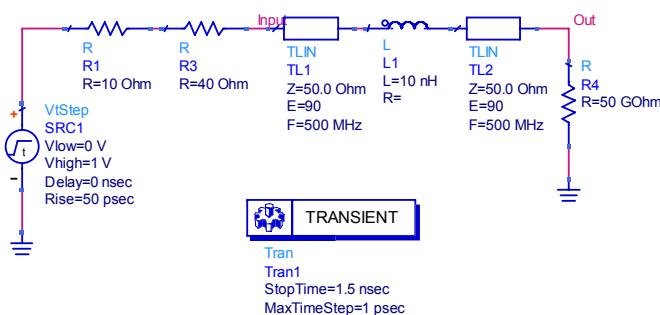

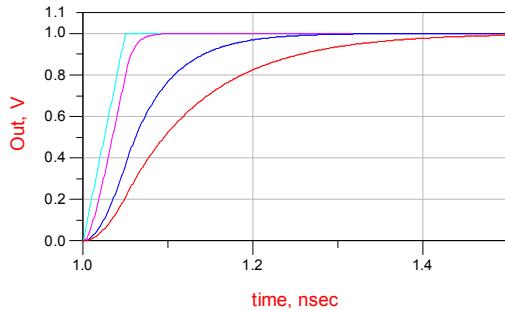

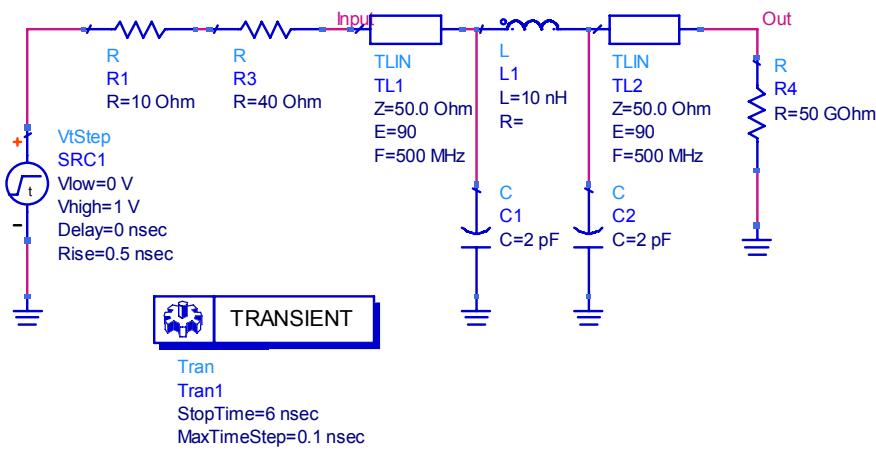

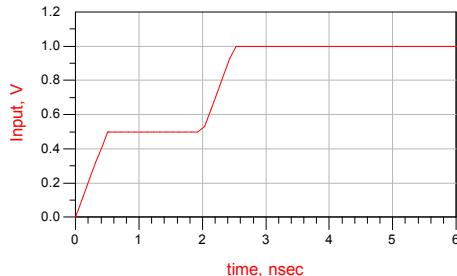

在传输线中，中间有一段阻抗的突变，如图 4-97 所示。当突变阻抗分别为  $25\Omega$ 、 $50\Omega$  和  $75\Omega$  时对输入输出波形进行仿真。

图 4-97 中间有一段阻抗突变的传输线

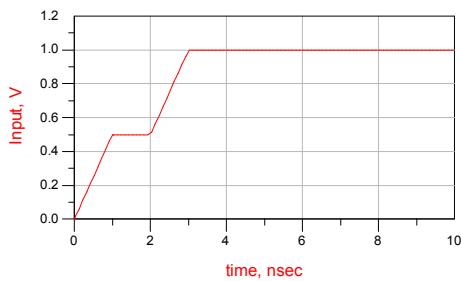

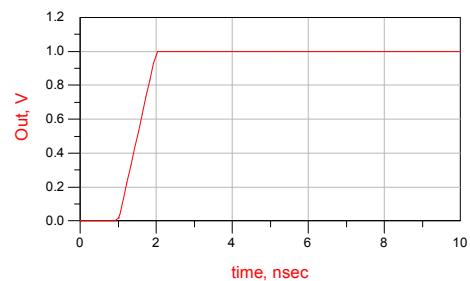

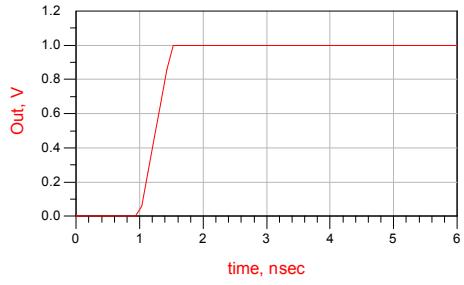

没有阻抗突变时输入、输出的仿真结果分别如图 4-98 和图 4-99 所示。

图 4-98 没有阻抗突变时输入的仿真结果

图 4-99 没有阻抗突变时输出的仿真结果

**技巧:** 在同一张图上显示三条线的实现方法

- 1) 先计算一固定值的结果, 如 TL2 的  $Z=75\Omega$  的结果。

- 2) 选中传输线 TL2, 如图 4-100 所示。

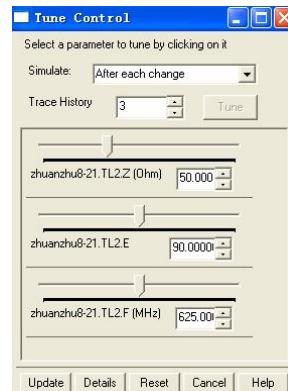

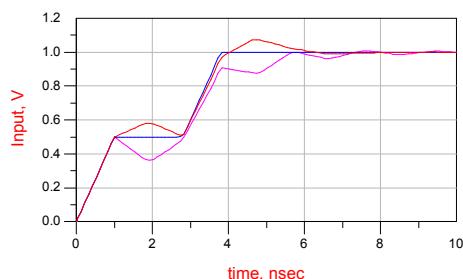

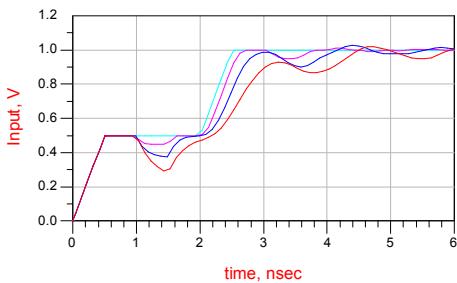

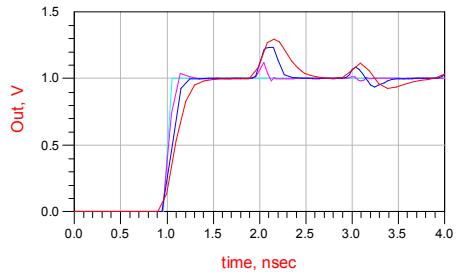

- 3) 在 Simulate 中单击 Tuning..., 改变 TL2 的值为  $50\Omega$  和  $25\Omega$ , 如图 4-101 所示, 即可得到三条曲线, 如图 4-102 和图 4-103 所示。

图 4-100 选中  $75\Omega$

图 4-101 改变 TL2 的值

图 4-102 不同突变阻抗的输入结果

图 4-103 不同突变阻抗的输出结果

中间传输线  $25\Omega$  和  $75\Omega$  的仿真结果如图 4-102 和图 4-103 所示, 向下凹是  $25\Omega$  的仿真结果, 向上凸是  $75\Omega$  的仿真结果。

#### 4.3.10 短串接传输线的反射 (续)

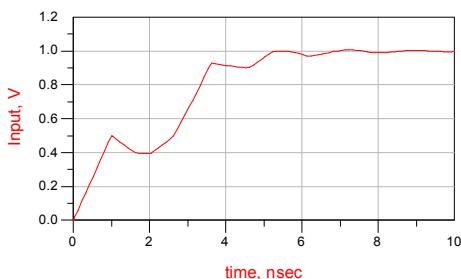

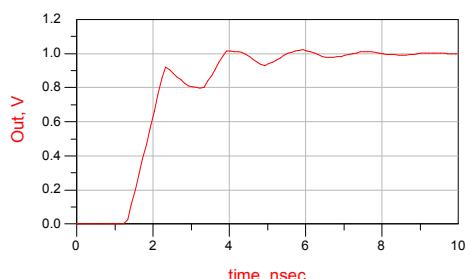

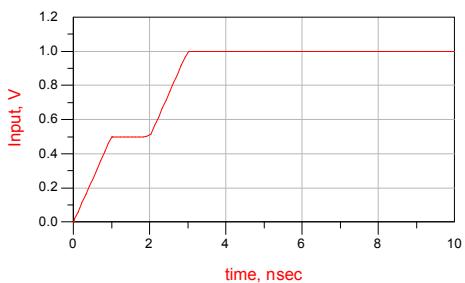

当突变阻抗固定为  $25\Omega$  而时延不同时, 对输入输出波形进行仿真, 如图 4-104 所示。

图 4-104 中间突变为  $25\Omega$  时的原理图

(1) TD=0%RT, 可设中间传输线 F=500GHz, 仿真结果如图 4-105 和图 4-106 所示。

图 4-105 TD=0%RT 时仿真的输入波形

图 4-106 TD=0%RT 时仿真的输出波形

(2) TD=20%RT=0.2ns, 可设中间传输线 F=1250MHz, 仿真结果如图 4-107 和图 4-108 所示。

图 4-107 TD=20%RT=0.2ns 时的输入波形

图 4-108 TD=20%RT=0.2ns 时的输出波形

(3) TD=30%RT=0.3ns, 可设中间传输线 F=833MHz, 仿真的波形如图 4-109 和图 4-110 所示。

图 4-109 TD=30%RT=0.3ns 时的输入波形

图 4-110 TD=30%RT=0.3ns 时的输出波形

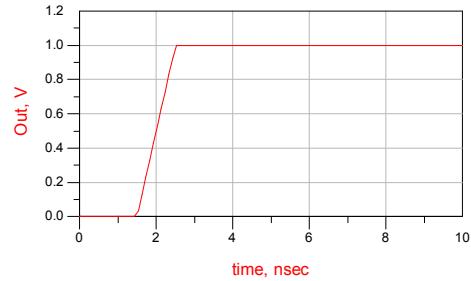

(4) TD=40%RT=0.4ns, 可设中间传输线 F=625MHz, 仿真结果如图 4-111 和图 4-112 所示。

图 4-111 TD=40%RT=0.4ns 时的输入波形

图 4-112 TD=40%RT=0.4ns 时的输出波形

#### 4.3.11 短桩线的反射

本节仿真短桩线传输线的反射。短桩线突变处阻抗为  $50\Omega$ , 时延不同时对输入输出波形进行仿真, 如图 4-113 所示。

图 4-113 短桩线突变的原理图

(1) TD=0%RT=0ns, 仿真结果如图 4-114 和图 4-115 所示。

图 4-114 TD=0%RT=0ns 时的输入波形

图 4-115 TD=0%RT=0ns 时的输出波形

(2) TD=20%RT=0.2ns, 可设中间传输线 F=1250MHz, 仿真结果如图 4-116 和图 4-117 所示。

(3) TD=40%RT=0.4ns, 可设中间传输线 F=625MHz, 仿真结果如图 4-118 和图 4-119 所示。

(4) TD=60%RT=0.6ns, 可设中间传输线 F=417MHz, 仿真结果如图 4-120 和图 4-121 所示。

图 4-116 TD=20%RT=0.2ns 时的输入波形

图 4-117 TD=20%RT=0.2ns 时的输出波形

图 4-118 TD=40%RT=0.4ns 时的输入波形

图 4-119 TD=40%RT=0.4ns 的输出波形

图 4-120 TD=60%RT=0.6ns 时的输入波形

图 4-121 TD=60%RT=0.6ns 时的输出波形

### 4.3.12 容性终端负载的反射

本节仿真容性终端负载的反射。电容终端负载分别为 0pF, 2pF, 5pF 和 10pF 时, 仿真输入输出波形。原理图如图 4-122 所示。

图 4-122 容性终端负载原理图

(1)  $C=0\text{pF}$  时, 仿真结果如图 4-123 和图 4-124 所示。

图 4-123  $C=0\text{pF}$  时的输入波形

图 4-124  $C=0\text{pF}$  时的输出波形

(2) 电容  $C=2\text{pF}$ 、 $5\text{pF}$ 、 $10\text{pF}$  时的仿真结果如图 4-125 和图 4-126 所示。

图 4-125 电容  $C=2\text{pF}$ 、 $5\text{pF}$ 、 $10\text{pF}$  时的输入波形

图 4-126 电容  $C=2\text{pF}$ 、 $5\text{pF}$ 、 $10\text{pF}$  时的输出波形

#### 4.3.13 连线中途的容性负载反射

本节仿真连线中途容性负载的反射。连线中途电容突变量分别为  $0\text{pF}$ 、 $2\text{pF}$ 、 $5\text{pF}$  和  $10\text{pF}$  时, 仿真输入输出波形。原理图如图 4-127 所示。

图 4-127 连线中途容性负载反射的原理图

(1) 突变电容为  $C=0\text{pF}$  时的仿真结果如图 4-128 和图 4-129 所示。

(2) 突变电容为  $C=2\text{pF}$ 、 $5\text{pF}$ 、 $10\text{pF}$  时的仿真结果如图 4-130 和图 4-131 所示。

图 4-128 突变电容为  $C=0\text{pF}$  时的输入波形图 4-129 突变电容为  $C=0\text{pF}$  时的输出波形图 4-130 突变电容为  $C=2\text{pF}$ 、 $5\text{pF}$ 、 $10\text{pF}$  时的输入结果图 4-131 突变电容为  $C=2\text{pF}$ 、 $5\text{pF}$ 、 $10\text{pF}$  时的输出结果

#### 4.3.14 容性时延累加

本节研究容性时延累加问题。当负载电容分别为  $0\text{pF}$ 、 $2\text{pF}$ 、 $5\text{pF}$  和  $10\text{pF}$  时，仿真输出端的电压波形。原理图如图 4-132 所示。

图 4-132 容性时延累加原理图

- (1)  $C=0\text{pF}$  时的输出仿真结果如图 4-133 所示。

- (2)  $C=2\text{pF}$ 、 $5\text{pF}$  和  $10\text{pF}$  时的输出仿真结果如图 4-134 所示。

#### 4.3.15 有载线

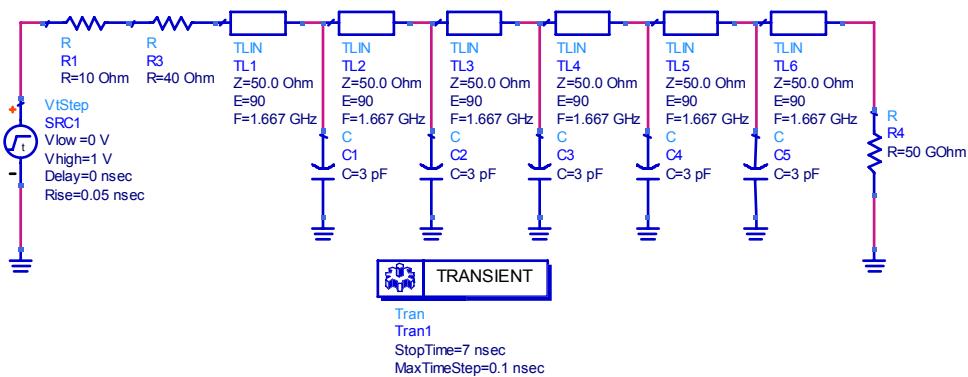

有载线上  $3\text{pF}$  电容间的时延为  $0.15\text{ns}$ ，仿真其上的反射信号，如图 4-135 所示。

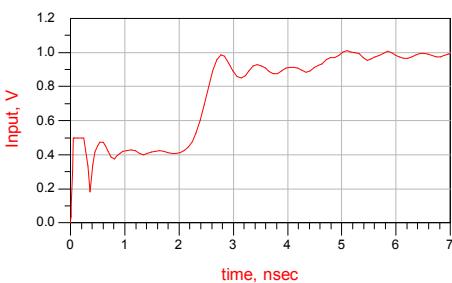

- (1)  $RT=0.05\text{ns}$  时的反射信号的波形如图 4-136 所示。

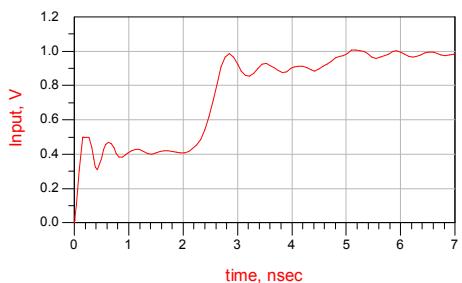

- (2)  $RT=0.15\text{ns}$  时的反射信号如图 4-137 所示。

图 4-133  $C=0\text{ pF}$  时的输出仿真结果

图 4-134  $C=2\text{ pF}$ 、 $5\text{ pF}$  和  $10\text{ pF}$  时的输出仿真结果

图 4-135 有载线的原理图

图 4-136  $RT=0.05\text{ ns}$  时的反射信号

图 4-137  $RT=0.15\text{ ns}$  时的反射信号

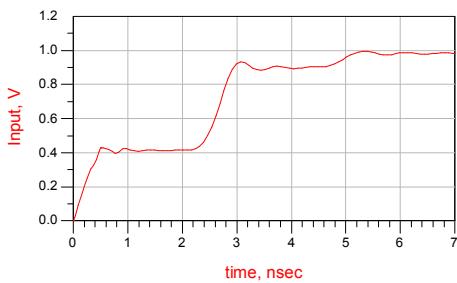

(3)  $RT=0.5\text{ ns}$  时的反射信号如图 4-138 所示。

图 4-138  $RT=0.5\text{ ns}$  时的反射信号

(4) 无载线情况, 无载线情况的原理图如图 4-139 所示。令所有的  $C=0\text{pF}$ , 上升时间=0.5ns, 仿真的反射信号如图 4-140 所示。

图 4-139 无载线的原理图

图 4-140 无载线的反射信号

#### 4.3.16 感性突变产生的反射

当传输线有感性突变时, 仿真输入和输出波形。原理图如图 4-141 所示。

图 4-141 感性突变产生的反射原理图

- (1) 电感  $L=0\text{nH}$  时的输入和输出波形如图 4-142 和图 4-143 所示。

- (2) 电感  $L=1\text{nH}$ 、 $5\text{nH}$ 、 $10\text{nH}$  时的结果如图 4-144 和图 4-145 所示。

图 4-142 电感  $L=0\text{nH}$  时的输入结果图 4-143 电感  $L=0\text{nH}$  时的输出结果

#### 4.3.17 感性时延累加

当感性突变为  $0\text{nH}$ 、 $1\text{nH}$ 、 $5\text{nH}$ 、 $10\text{nH}$  时，仿真接收信号的时延累加。原理图如图 4-146 所示，只需要在图 4-141 基础上修改截止时间和时间步长即可。

图 4-146 感性时延累加原理图

(1) 电感  $L=0\text{nH}$  时的结果如图 4-147 所示。

图 4-147 电感  $L=0\text{nH}$  时的结果

(2) 电感 L=1nH、5nH、10nH 时的结果如图 4-148 所示。

图 4-148 电感 L=1nH、5nH、10nH 时的结果

#### 4.3.18 补偿

当有感性突变时，可以采取补偿的方法。仿真的原理图如图 4-149 所示。

图 4-149 用于感性突变的补偿电路

(1) 没有接插件的仿真结果如图 4-150 和图 4-151 所示。

图 4-150 没有接插件的输入结果

图 4-151 没有接插件的输出结果

(2) 有接插件没有补偿电容的结果如图 4-152 和图 4-153 所示。

(3) 有接插件有补偿电容的结果如图 4-154 和图 4-155 所示。

图 4-152 有接插件没有补偿电容的输入结果

图 4-153 有接插件没有补偿电容的输出结果

图 4-154 有接插件有补偿电容的输入结果

图 4-155 有接插件有补偿电容的输出结果

## 4.4 考虑损耗时的仿真

### 4.4.1 信号的损耗

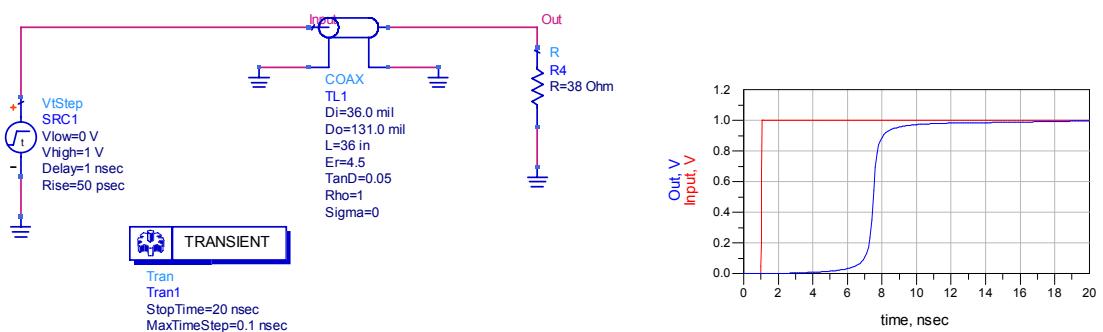

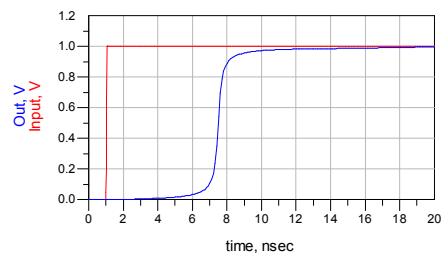

经过  $50\Omega$ 、36in 长的传输线的输入和输出信号。原理图如图 4-156 所示。注意参数设置。仿真的输入信号和输出信号如图 4-157 所示。

图 4-156 信号的损耗原理图

图 4-157 有损耗传输线的输入信号

和输出信号

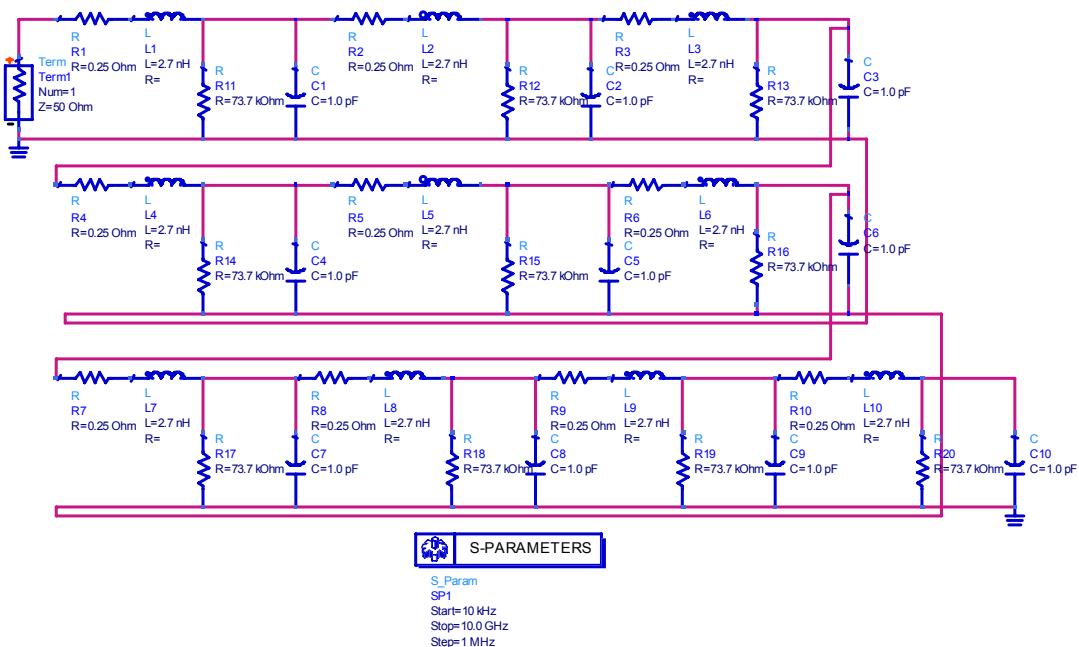

### 4.4.2 有损耗传输线的建模

- 模型带宽=2GHz，线时延 0.5ns，物理长度=3in，最小节数 n=10。

- 每节长度=0.3in，因为电感 L 大约=9nH/in，所以每节电感  $L_L=2.7\text{nH}$ 。

- 在低损耗区  $R = \sqrt{\frac{L}{C_L}} = 50$ , 得到  $C_L = 1.08\text{pF}$ 。

单位长度交流电阻  $R_L = \frac{1 \times 10^{-4}}{w} \sqrt{\omega}$ ,  $w=3$ ,  $f=100\text{MHz}$ , 代入参数得  $R_L=0.835\Omega$ , 每节电阻  $=0.25\Omega$ 。

- 电导  $G = \omega \tan(\delta)C$ ,  $G = 2\pi f \times 0.02 \times 1.08 \times 10^{-12} = 1.36 \times 10^{-5}$ 。

依据以上参数建立的等效电路模型如图 4-158 所示。

图 4-158 有损耗线的等效电路模型

带宽到 10GHz 的结果如图 4-159 所示。

带宽到 2GHz 的结果如图 4-160 所示。

图 4-159 带宽到 10GHz 的结果

图 4-160 带宽到 2GHz 的结果

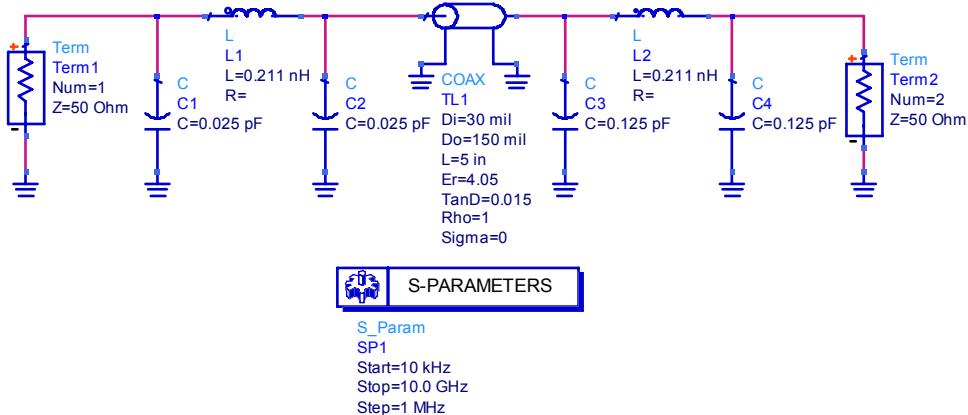

#### 4.4.3 传输线测试模型

实际传输线测试结构的原理图如图 4-161 所示。

图 4-161 实际传输线测试结构的理想电路模型

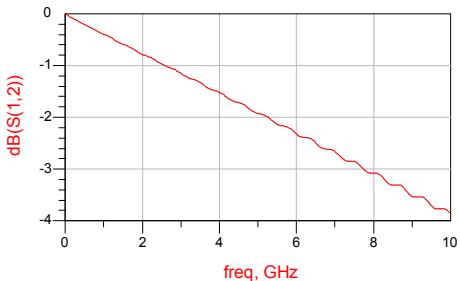

仿真得到的插入损耗幅值如图 4-162 所示。

图 4-162 插入损耗幅值

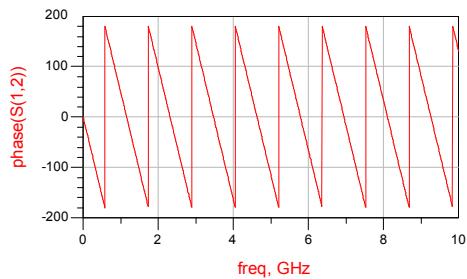

仿真得到的插入损耗相位如图 4-163 所示。

图 4-163 插入损耗相位

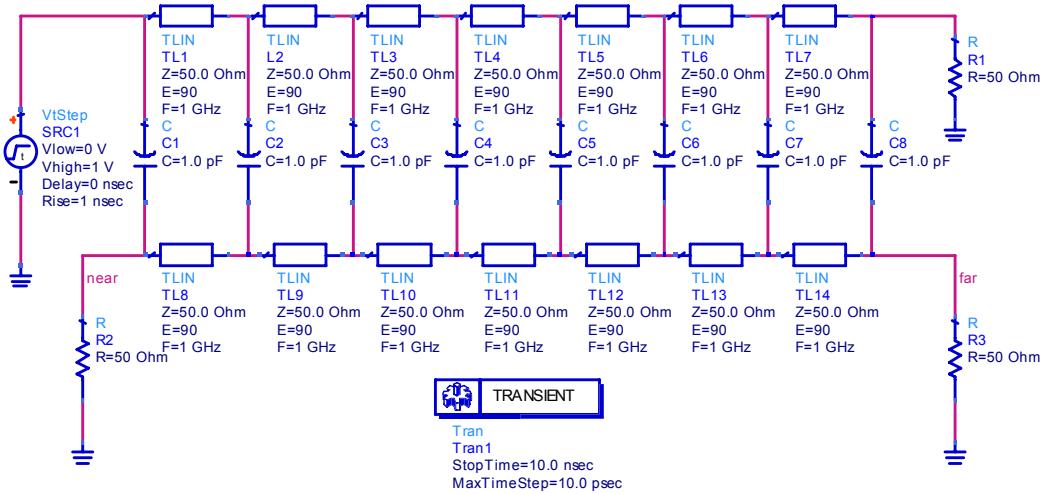

## 4.5 传输线的串扰仿真

### 4.5.1 容性耦合电流

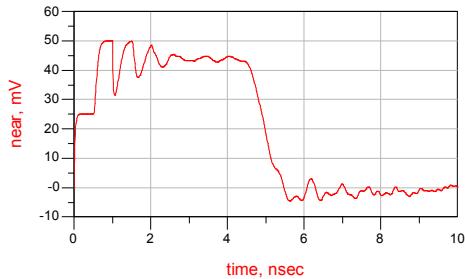

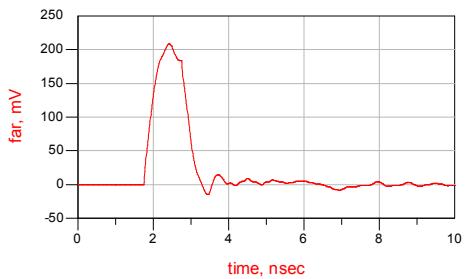

只考虑容性耦合时，两条耦合线的等效电路模型。用 ADS 建立的等效电路模型如图 4-164 所示。

仿真得到的静态线近端串扰如图 4-165 所示。

图 4-164 容性耦合等效电路模型

静态线远端串扰如图 4-166 所示。

图 4-165 静态线近端串扰

图 4-166 静态线远端串扰

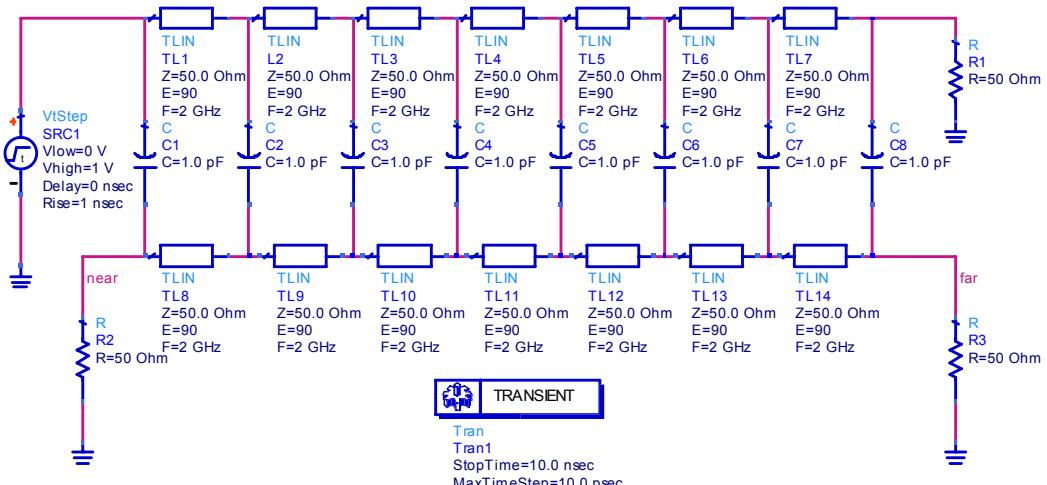

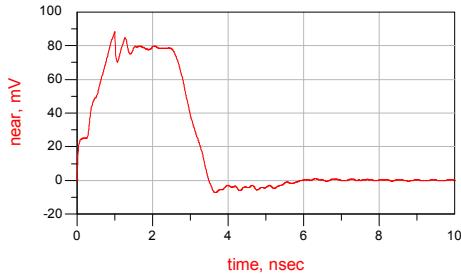

当传输线的频率  $f=2\text{GHz}$  时的等效电路如图 4-167 所示。

图 4-167 传输线的频率  $f=2\text{GHz}$  时的等效电路模型

仿真得到的静态线近端串扰如图 4-168 所示。

静态线近端串扰如图 4-169 所示。

图 4-168 静态线近端串扰

图 4-169 静态线远端串扰

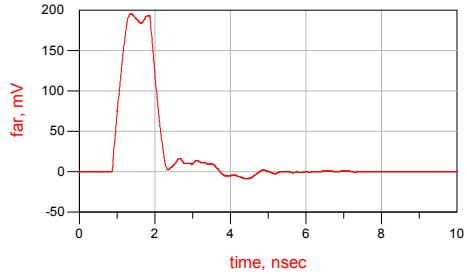

#### 4.5.2 感性耦合电流

只考虑感性耦合，当信号沿着动态线传输时，感应的电流回路分别沿前向和后向传播。原理图如图 4-170 所示。

图 4-170 感性耦合电路模型

在原理图中注意参数设置：互感值要小于任何一个自感值，互感单位要选择与自感单位一致。仿真得到的近端串扰如图 4-171 所示。

图 4-171 近端串扰

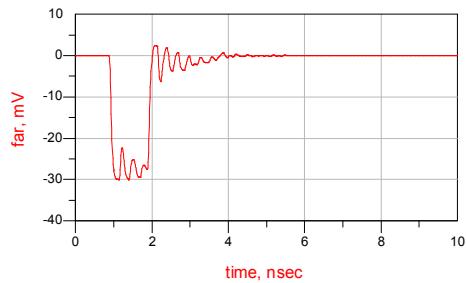

远端串扰如图 4-172 所示。

图 4-172 远端串扰

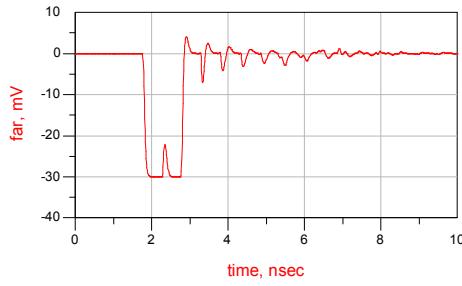

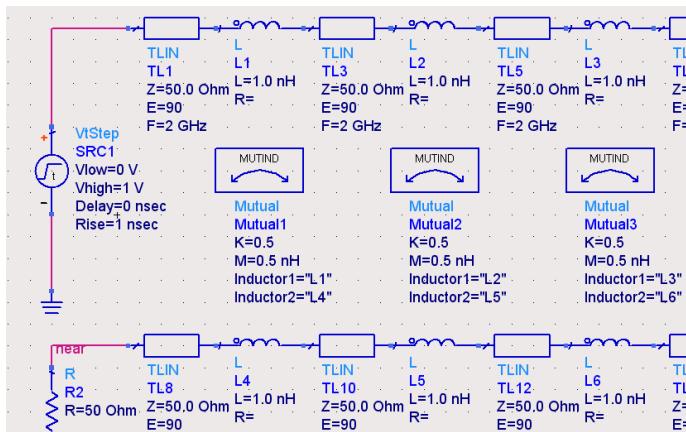

当传输线的频率  $f=2\text{GHz}$  时的等效电路如图 4-173 所示。

图 4-173 传输线的频率  $f=2\text{GHz}$  时的等效电路

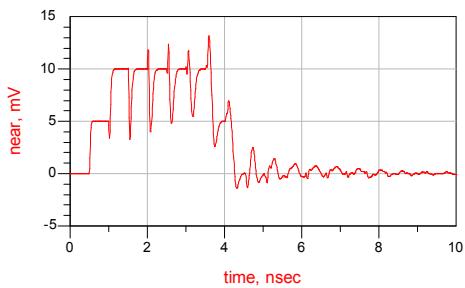

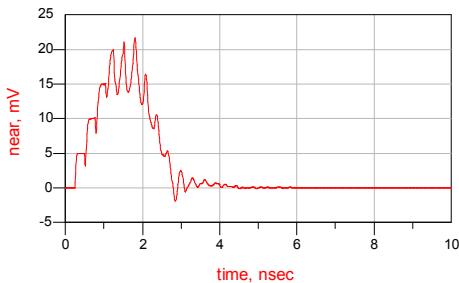

近端串扰如图 4-174 所示。

远端串扰如图 4-175 所示。

图 4-174 近端串扰

图 4-175 远端串扰

## 4.6 差分对仿真

### 4.6.1 差分对的端接

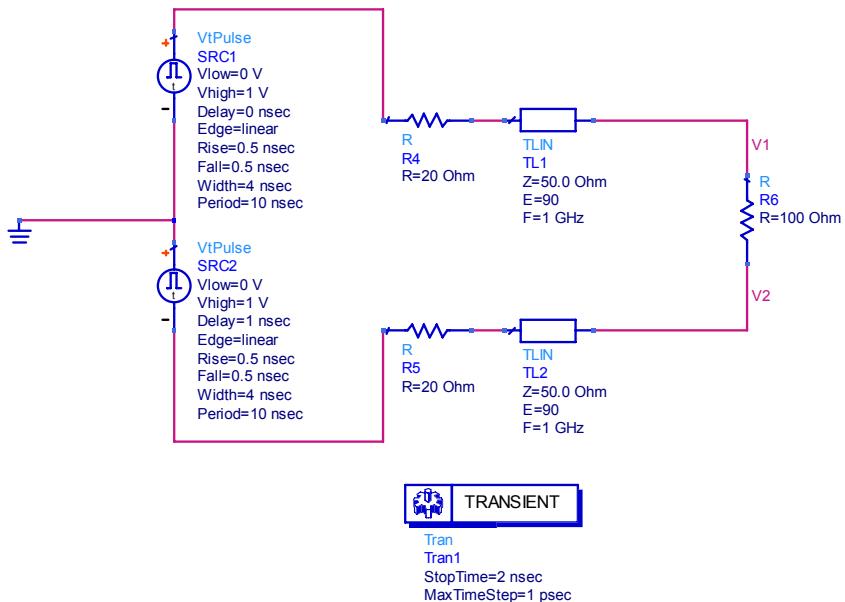

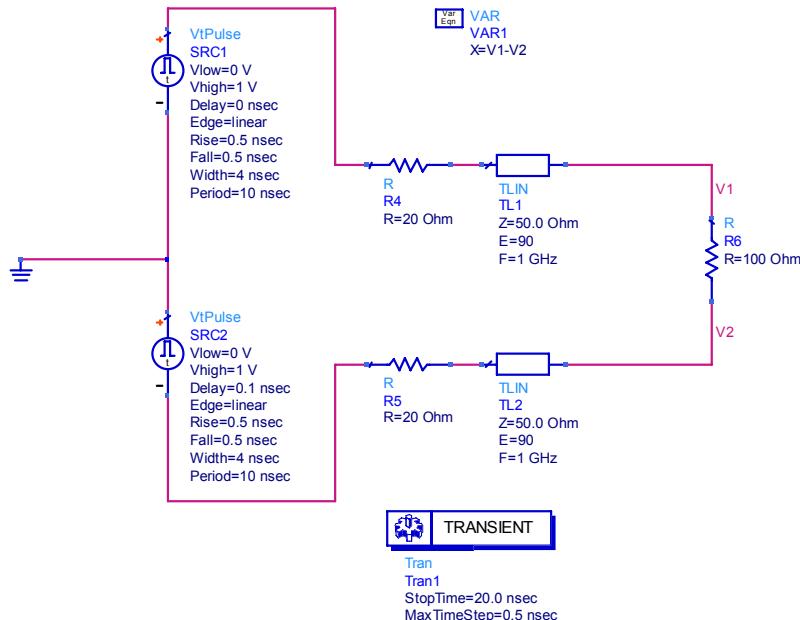

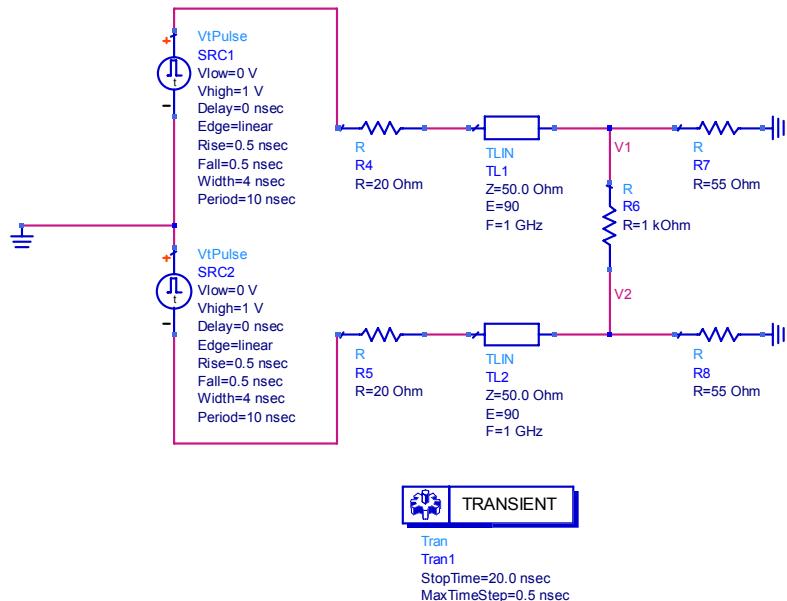

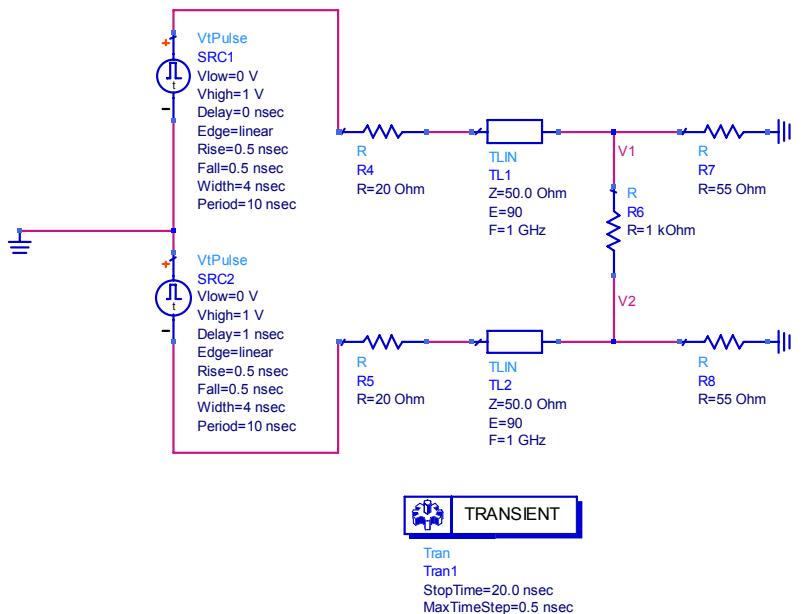

当差分对末端进行端接和不端接时，仿真差分信号。所建立的等效电路模型如图 4-176 所示。

图 4-176 差分对的电路模型

当差分对端接匹配时的结果如图 4-177 所示。

图 4-177 差分对端接时的结果

差分对末端开路时的结果如图 4-178 所示。

图 4-178 差分对末端开路时的结果

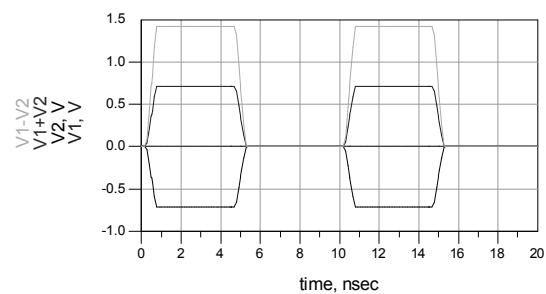

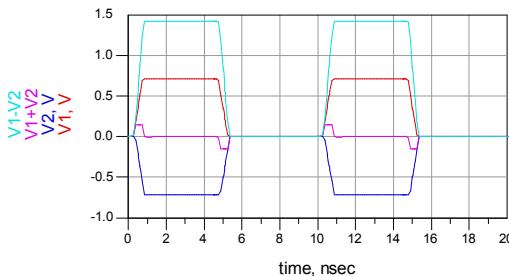

#### 4.6.2 差分信号向共模信号的转化

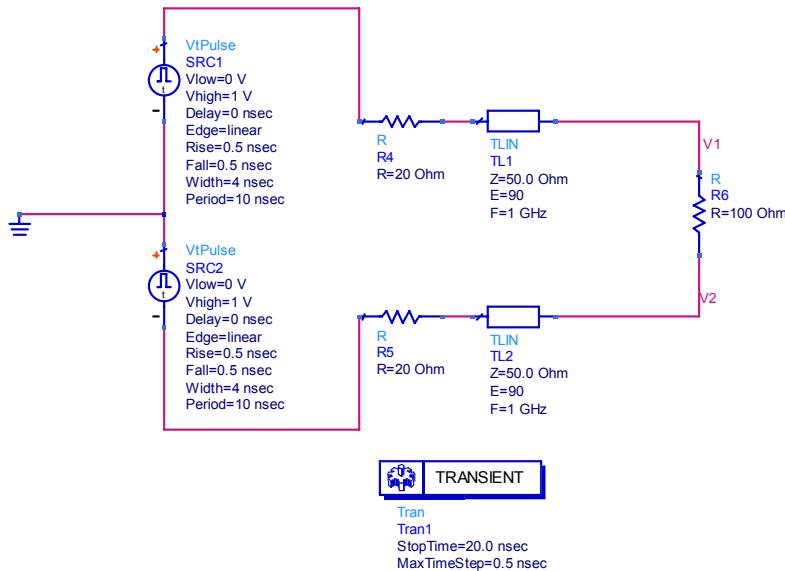

当驱动器错位从上升时间的 20% 变化到 2 倍时, 差分信号的变化情况。原理图如图 4-179 所示。

图 4-179 差分信号向共模信号的转化原理图 ( $\Delta t=2RT$  时的图)

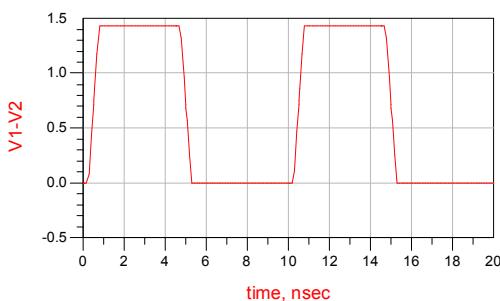

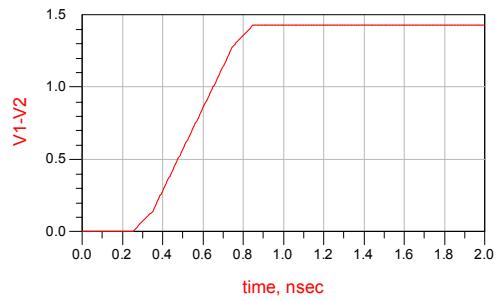

(1)  $\Delta t=20\%RT$  的仿真结果如图 4-180 所示。

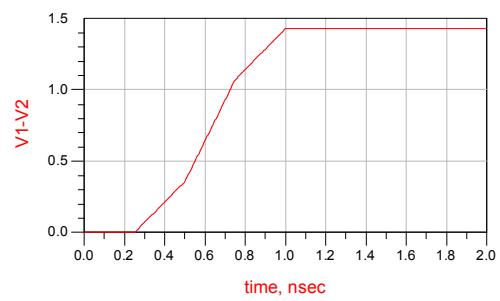

(2)  $\Delta t=50\%RT$  的仿真结果如图 4-181 所示。

图 4-180  $\Delta t=20\%RT$  的仿真结果图 4-181  $\Delta t=50\%RT$  的仿真结果

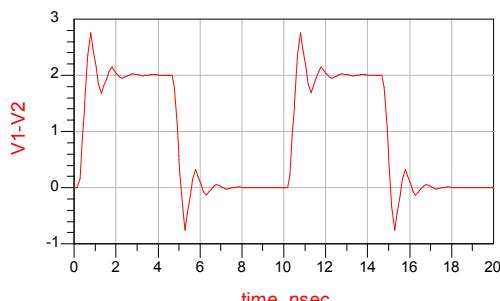

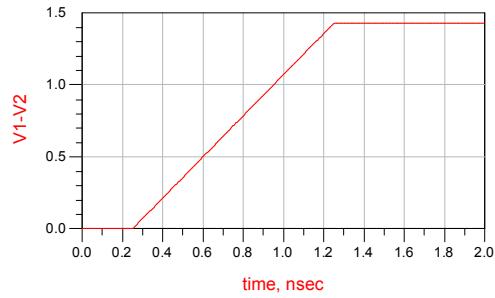

(3)  $\Delta t=RT$  的仿真结果如图 4-182 所示。

(4)  $\Delta t=2RT$  的仿真结果如图 4-183 所示。

图 4-182  $\Delta t=RT$  的仿真结果图 4-183  $\Delta t=2RT$  的仿真结果

### 4.6.3 差分对一根信号线接容性负载时的情况

当一根信号线由于感受到了测试焊盘而产生一个容性负载时，另一根却没有，差分信号就会失真。本节仿真这种情况。原理图如图 4-184 所示。

图 4-184 差分对一根信号线接容性负载的原理图

没有接容性负载时的仿真结果如图 4-185 所示。

图 4-185 没有接容性负载时的仿真结果

接容性负载时的仿真结果如图 4-186 所示。

图 4-186 接容性负载时的仿真结果

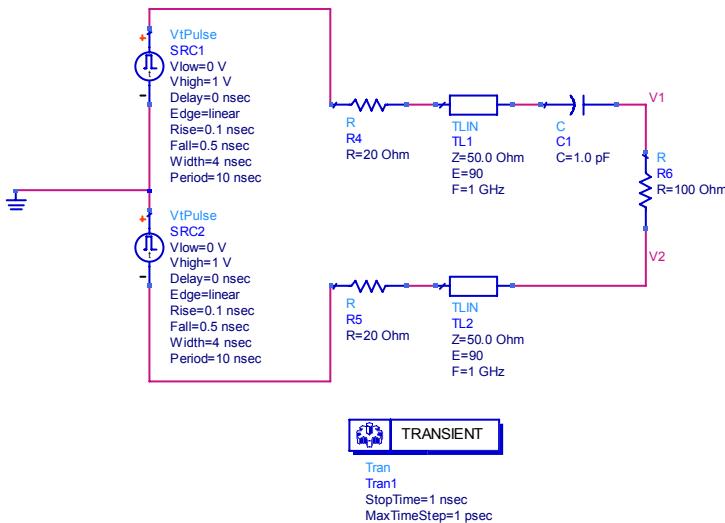

#### 4.6.4 差分对端接对共模信号的影响

一个小的错位可能不会影响到差分信号，但对共模信号可能产生比较显著的影响。本节仿真这种情况。原理图如图 4-187 所示。

图 4-187 差分对端接对共模信号的影响

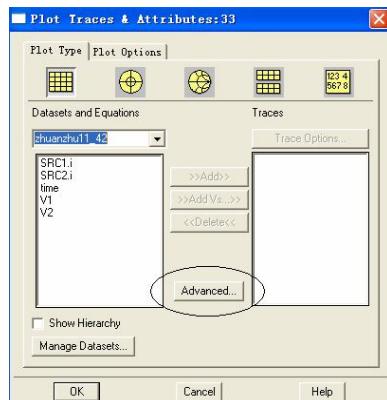

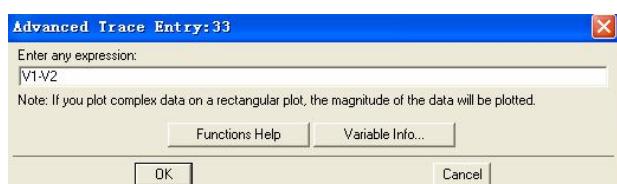

在求差分信号时，在 Plot Type 选项卡中单击 Advanced 按钮可以进行曲线的加减运算，如图 4-188 和图 4-189 所示。

图 4-188 单击 Advanced 按钮

图 4-189 输入 V1-V2

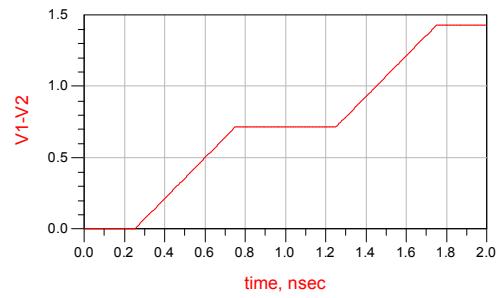

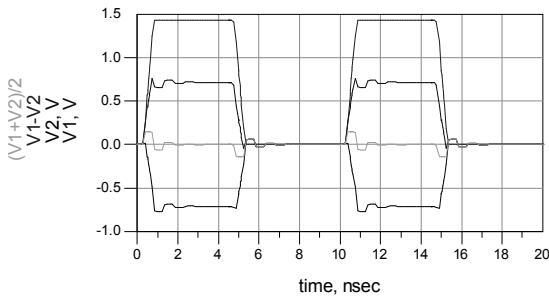

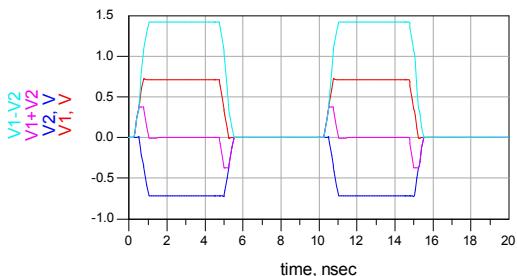

差分信号和共模信号如图 4-190 所示。

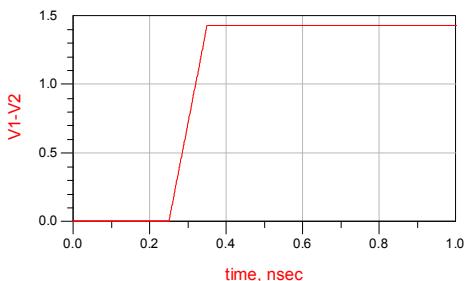

#### 4.6.5 同时端接共模和差模

驱动器没有错位，同时端接共模和差模。原理图如图 4-191 所示。在这种情况下，共模消失了。

图 4-190 差分信号和共模信号

图 4-191 驱动器没有错位，同时端接共模和差模

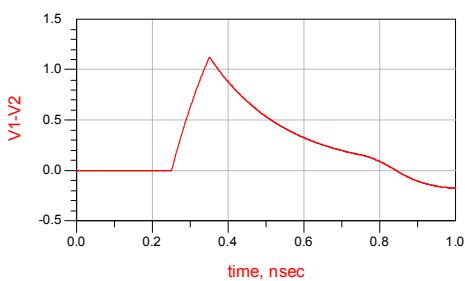

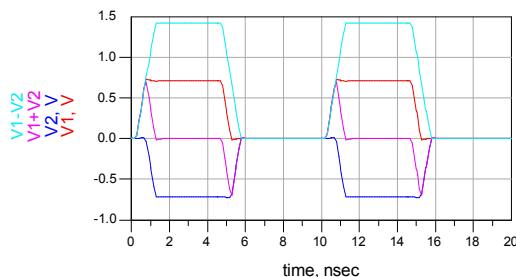

仿真得到的差分信号和共模信号如图 4-192 所示。

图 4-192 差分信号和共模信号

#### 4.6.6 同时端接共模和差模有错位

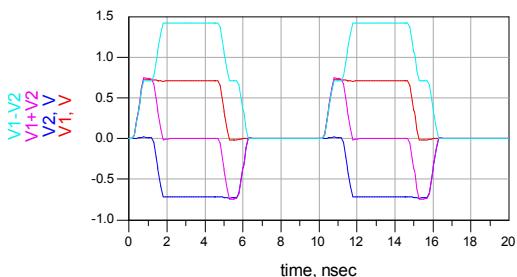

同时端接共模和差模，有错位，利用图 4-191，只改变错位，如图 4-193 所示。

图 4-193 驱动器有错位，同时端接共模和差模

错位=20%RT 的仿真结果如图 4-194 所示。

错位=50%RT 的仿真结果如图 4-195 所示。

图 4-194 错位=20%RT 的仿真结果

图 4-195 错位=50%RT 的仿真结果

错位=100%RT 的仿真结果如图 4-196 所示。

错位=200%RT 的仿真结果如图 4-197 所示。

图 4-196 错位=100%RT 的仿真结果

图 4-197 错位=200%RT 的仿真结果